# **LOW POWER SCHOTTKY**

MOTOROLA Semiconductors

| Circuit | Char | acte | ristics | 1 |

|---------|------|------|---------|---|

|         |      |      |         |   |

- **Design Considerations 2**

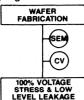

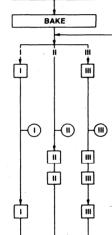

- **Selection Information** 3

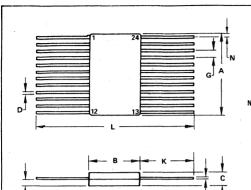

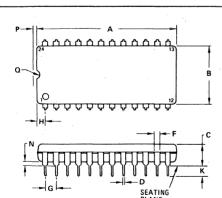

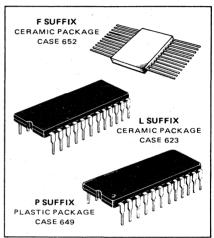

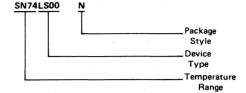

- Data Sheets 4

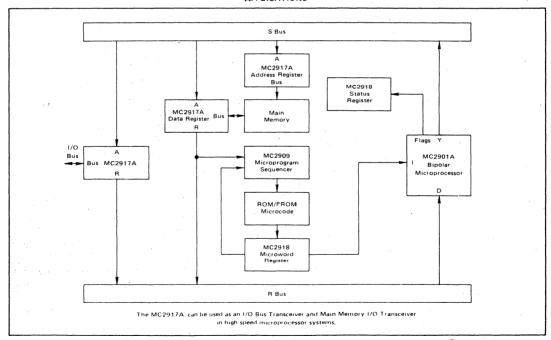

- M2900 Processor Family and Memories 5

- Reliability Data 6

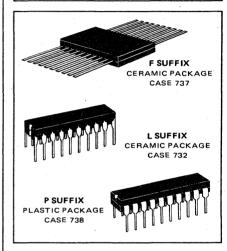

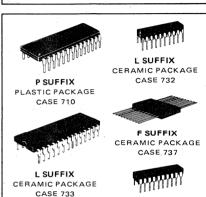

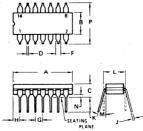

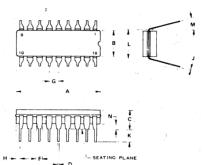

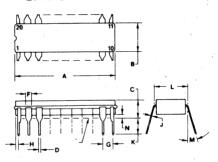

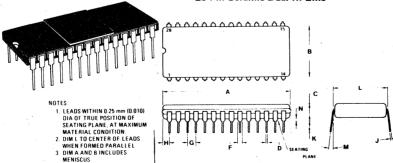

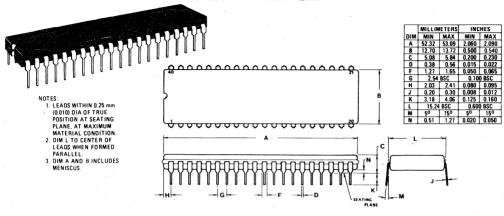

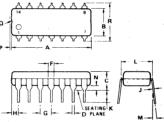

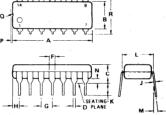

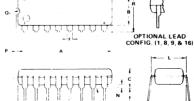

- Ordering Information and Package Outlines

# LOW-POWER SCHOTTKY TTL

Prepared by Technical Information Center

This book presents technical data for a broad line of low-power Schottky TTL integrated circuits. Complete specifications for the individual circuits are provided in the form of data sheets. In addition, the general characteristics and design considerations of this popular family are discussed, and selection guides are included to simplify the task of choosing the best combination of circuits for a system.

The information in this book has been carefully checked and is believed to be reliable; however, no responsibility is assumed for inaccuracies. Furthermore, this information does not convey to the purchaser of microelectronic devices any license under the patent rights of any manufacturer.

This information is published with permission of Fairchild Camera and Instrument Corp. under their copyright. In addition, many original Motorola circuits have been added to the Fairchild information.

© 1977, Semiconductor Components Group,

"All Rights Reserved"

# CONTENTS

|                                                                                                                                                                                                                          | Page                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| NUMERICAL INDEX OF DEVICES                                                                                                                                                                                               | ii .                                      |

| CHAPTER 1 — CIRCUIT CHARACTERISTICS.  Input Configuration  Output Configuration  Output Characteristics  AC Switching Characteristics  Absolute Maximum Ratings                                                          | 1-1<br>1-2<br>1-3<br>1-5<br>1-6<br>1-8    |

| CHAPTER 2 — DESIGN CONSIDERATIONS  Supply Voltage and Temperature Range  Noise Immunity/Noise Margins  Fan-In and Fan-Out  Wired-OR Applications  Unused Inputs  Interconnection Delays  Definition of Symbols and Terms | . 2-2<br>. 2-3<br>. 2-4<br>. 2-5<br>. 2-5 |

| CHAPTER 3 – SELECTION INFORMATION                                                                                                                                                                                        | . 3-1                                     |

| CHAPTER 4 – DATA SHEETS                                                                                                                                                                                                  | . 4-1                                     |

| CHAPTER 5 - M2900 PROCESSOR FAMILY AND MEMORIES                                                                                                                                                                          | . 5-1                                     |

| CHAPTER 6 — RELIABILITY DATA  High-Reliability Standard Programs  The "Better" Program  "RAP" Reliability Audit Program                                                                                                  | . 6-1<br>. 6-2<br>. 6-4<br>. 6-6          |

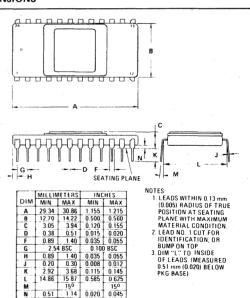

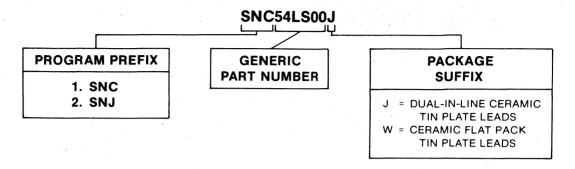

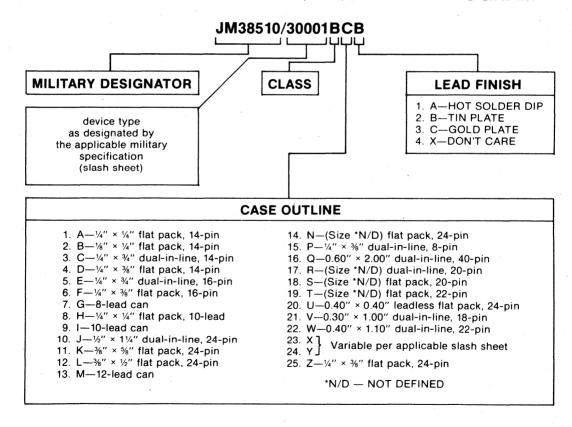

| CHAPTER 7 – ORDERING INFORMATION AND PACKAGE OUTLINES  SN54LS00/74LS00 Series                                                                                                                                            | . 7-1<br>. 7-2<br>. 7-6                   |

| Memories  Package Outlines                                                                                                                                                                                               | . /-/                                     |

# NUMERICAL INDEX OF DEVICES

| Device        | Description                                                 |                |

|---------------|-------------------------------------------------------------|----------------|

| 54LS/74LS00   | 2-121                                                       | Page           |

| 54LS/74LS01   | Quad 2-Input NAND Gate Quad 2-Input NAND Gate               | 1-4            |

| 54LS/74LS02   |                                                             |                |

| 54LS/74LS03   |                                                             |                |

|               |                                                             |                |

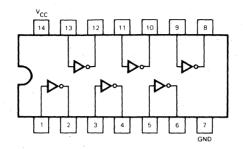

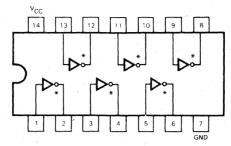

| 54LS/74LS04   | Hex Inverter                                                | 4-:            |

| 54LS/74LS05   | Hex Inverter (Open Collector)                               |                |

| 54LS/74LS08   | Overlast (Open Collector)                                   | 4-7            |

| 54LS/74LS09   | Quad 2-Input AND Gate Quad 2-Input AND Gate (Open Colleges) | 4.9            |

| 54LS/74LS10   |                                                             |                |

| 54LS/74LS10   | Triple 3-Input NAND Gate Triple 3-Input AND Gate            | 4 10           |

| 54L5//4L511   | Triple 3-Input AND Gate                                     | 4-10           |

| 54LS/74LS12   |                                                             |                |

| 54LS/74LS13   | Triple 3-Input NAND Gate                                    | 4-12           |

| 54LS/74LS14   |                                                             |                |

| 54LS/74LS15   |                                                             |                |

| 54LS/74LS20   |                                                             |                |

| 04L3/74L320   | Dual 4-Input NAND Gate                                      | 4.16           |

| EAL 9/741 001 |                                                             |                |

| 54LS/74LS21   | Dual 4-Input AND Gate                                       | 4 17           |

| 54LS/74LS22   |                                                             |                |

| 54LS/74LS26   |                                                             |                |

| 54LS/74LS27   | Triple 3-Input NOR Gate                                     | 4-19           |

| 54LS/74LS28   | QUAD 2-Input NOR Buffer.                                    | 4-20           |

| 541 0/341 aa- |                                                             | 4-21           |

| 54LS/74LS30   | 8-Input NAND Gate                                           |                |

| 54LS/74LS32   | Input Off Gale                                              |                |

| 54LS/74LS33   |                                                             |                |

| 54LS/74LS37   | QUAD 2-Input NAND Buffer                                    | 4-24           |

| 54LS/74LS38   | QUAD 2-Input NAND Buffer (Open Collector)                   | 4-25           |

| E41.0/341.040 |                                                             |                |

| 54LS/74LS40   | Dual 4-Input NAND Buffer.                                   | 4.07           |

| 54LS/74LS42   | 1 Of 10 Decoder                                             |                |

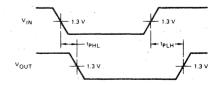

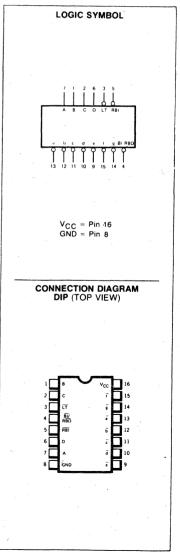

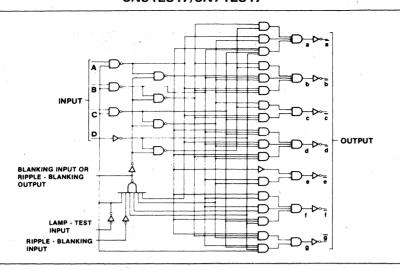

| 54LS/74LS47   | ob to / begine it Decouer/11/11/er (Linen (Collector)       |                |

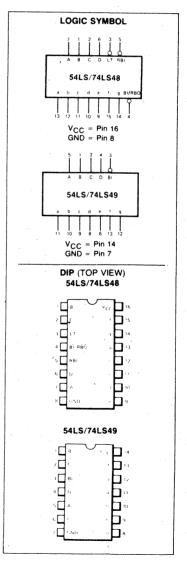

| 54LS/74LS48   | 505 to 7-segment Decoder/Driver                             |                |

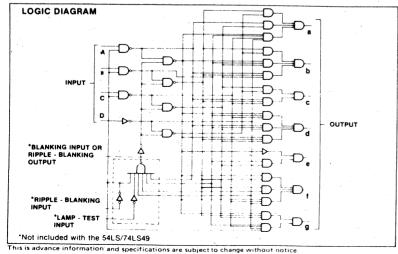

| 54LS/74LS49   | BCD to 7-Segment Decoder/Driver (Open Collector)            | 4-34           |

| 54LS/74LS51   |                                                             |                |

| 54LS/74LS54   | Dual AND-OR-Invert Gate                                     | 4.38           |

| 54LS/74LS55   |                                                             |                |

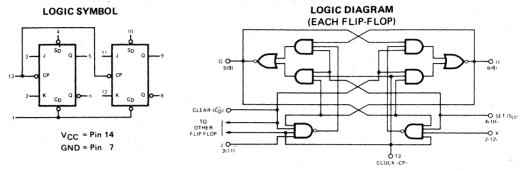

| 54LS/74LS73A  | = Tride + Hiput                                             |                |

|               | 2 ddi 317 i iip-i 10p                                       |                |

| 54LS/74LS74A  | Dual D Flip-Flop                                            | 4-41           |

| 54LS/74LS75   |                                                             |                |

| 53LS/74LS76A  | 4-Bit Bi-Stable Latch DUAL JK Flin-Flon                     | 4-46           |

| 54LS/74LS76A  |                                                             | 4 50           |

|               | 4-Bit Bi-Stable Latch                                       | 1 16           |

| 54LS/74LS78A  | DOAL 3K FIID-FIOD                                           |                |

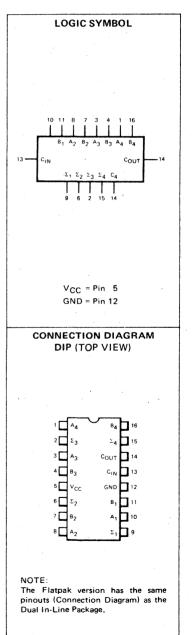

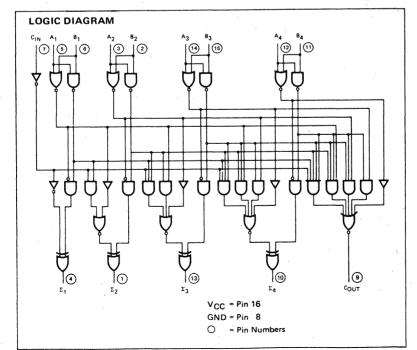

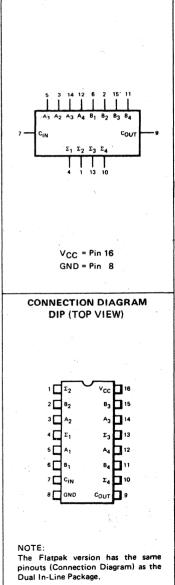

| 54LS/74LS83A  | 4-Bit Full Adder                                            | 4-55           |

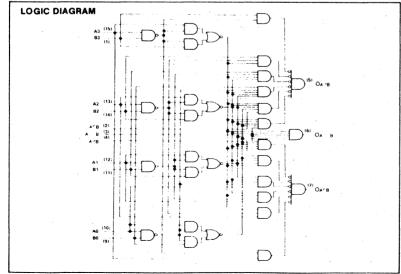

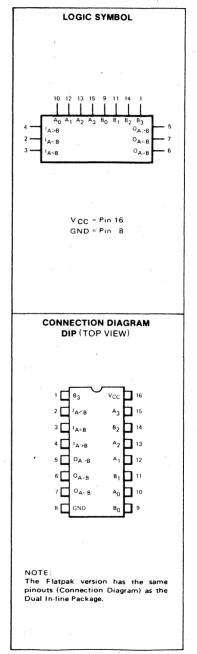

| 54LŠ/74LS85   |                                                             |                |

|               | 4-Bit Magnitude Comparator                                  | 4.50           |

| 54LS/74LS86   | adda Exclusive OH Gate                                      |                |

| 54LS/74LS89   |                                                             |                |

| 54LS/74LS90   |                                                             |                |

| 54LS/74LS92   | Divide-by-12 Counter                                        | 4-04<br>4-61   |

| 54LS/74LS93   |                                                             |                |

|               | 4-Bit Binary Counter                                        | 4-64           |

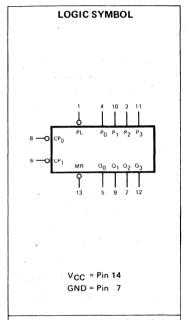

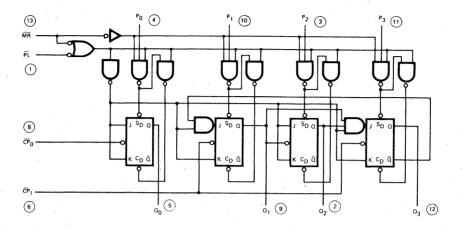

| 54LS/74LS95B  | T Dit Simit megister                                        | 4 = 0          |

| 4LS/74LS107A  |                                                             |                |

| 4LS/74LS109A  |                                                             |                |

| 4LS/74LS112A  | Dual JK Edge-Triggered Flip-Flop                            | . 4-/5<br>4-77 |

|               |                                                             |                |

### NUMERICAL INDEX OF DEVICES (Cont'd)

| Device           | Description                                          | Page    |

|------------------|------------------------------------------------------|---------|

| 54LS/74LS113A    | Dual JK Edge-Triggered Flip-Flop                     | 4-79    |

| 54LS/74LS114A    | Dual JK Edge-Triggered Flip-Flop                     | 4-81    |

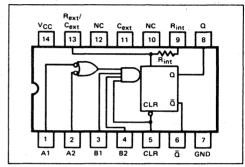

| 54LS/74LS122     | Retriggerable Monostable Multivibrators              | 4.83    |

| 54LS/74LS123     | Retriggerable Monostable Multivibrators              | 4.03    |

|                  | Dual Valence Controlled Conflictions                 | . 4-00  |

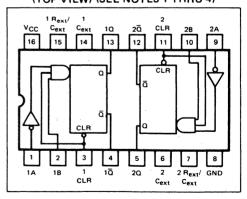

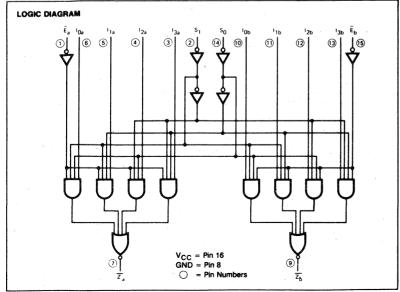

| 54LS/74LS124     | Dual Voltage-Controlled Oscillators                  | 4-84    |

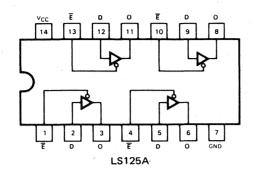

| E41 6/741 610E A | Overal 2 Cares Buffer / LOW Freshie                  | . 4 0E  |

| 54LS/74LS125A    | Quad 3-State Buffer (LOW Enable)                     | 4-00    |

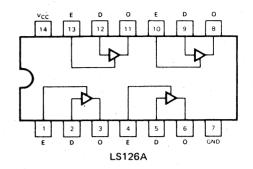

| 54LS/74LS126A    | Quad 3-State Buffer (HIGH Enable)                    | 4-85    |

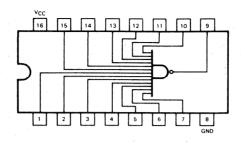

| 54LS/74LS132     | Quad 2-Input Schmitt Trigger                         | 4-87    |

| 54LS/74LS133     | 13-Input NAND Gate                                   | . 4-89  |

| 54LS/74LS136     | Quad Exclusive OR (Open Collector)                   | . 4-90  |

|                  |                                                      | 4.04    |

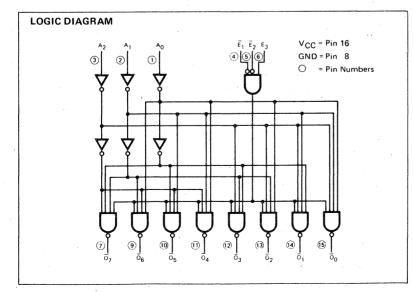

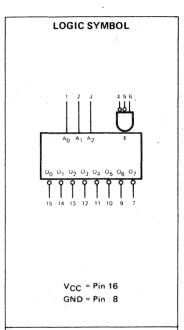

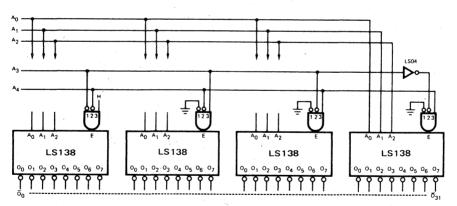

| 54LS/74LS138     | 1-of-8 Decoder/Demultiplexer                         | . 4-91  |

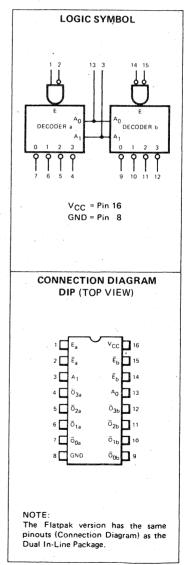

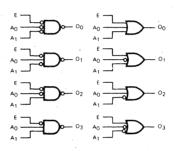

| 54LS/74LS139     | Dual 1-of-4 Decoder/Demultiplexer                    | . 4-94  |

| 54LS/74LS145     | BCD-to-Decimal Decoder                               | . 4-97  |

| 54LS/74LS151     | 8-Input Multiplexer                                  | 4-100   |

| 54LS/74LS153     | Dual 4-Input Multiplexer                             | 4-103   |

|                  |                                                      |         |

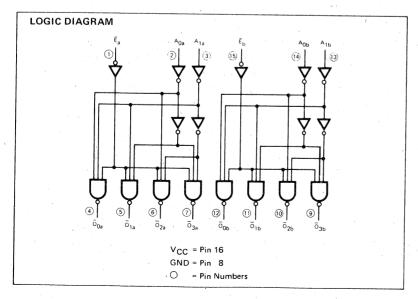

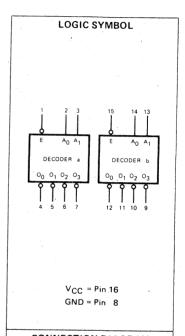

| 54LS/74LS155     | Dual 1-of-4 Decoder                                  | 4-106   |

| 54LS/74LS156     | Dual 1-of-4 Decoder (Open Collector)                 | 4-106   |

| 54LS/74LS157     | Quad 2-Input Multiplexer (Non-inverting)             | 4-110   |

| 54LS/74LS158     | Quad 2-Input Multiplexer (Inverting)                 | 4-113   |

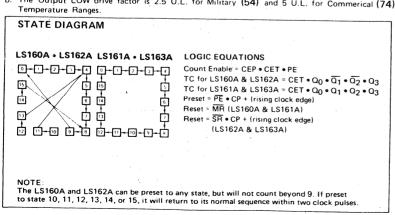

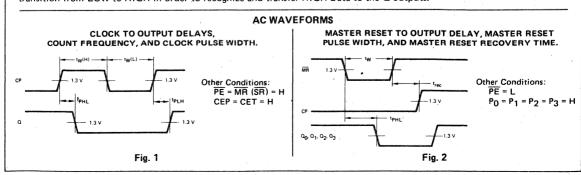

| 54LS/74LS160A    | BCD Decade Counter, Asynchronous Reset (9310 Type)   |         |

|                  |                                                      |         |

| 54LS/74LS161A    | 4-Bit Binary Counter, Asynchronous Reset (9316 Type) | 4-116   |

| 54LS/74LS162A    | BCD Decade Counter, Synchronous Reset                | 4-116   |

| 54LS/74LS163A    | 4-Bit Binary Counter, Synchronous Reset              |         |

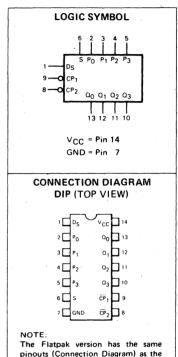

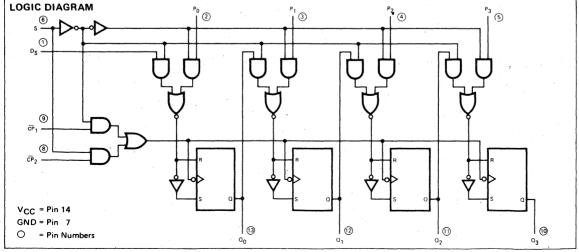

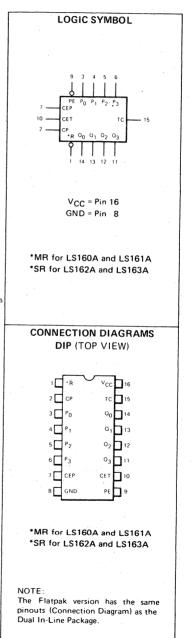

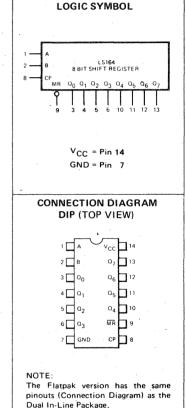

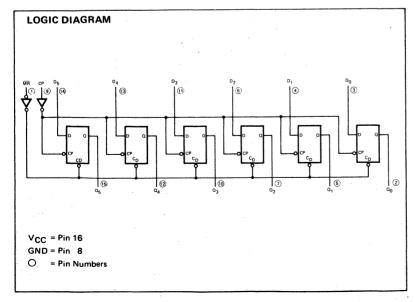

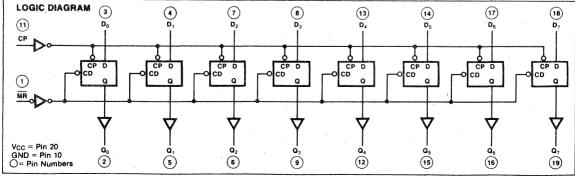

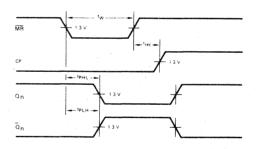

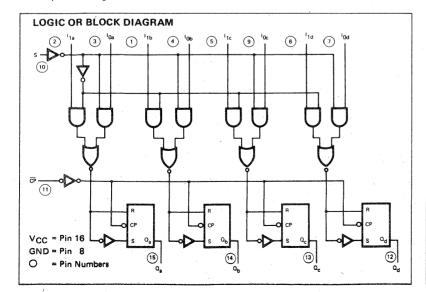

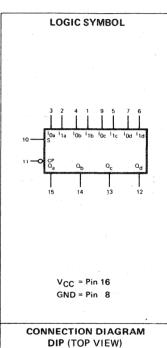

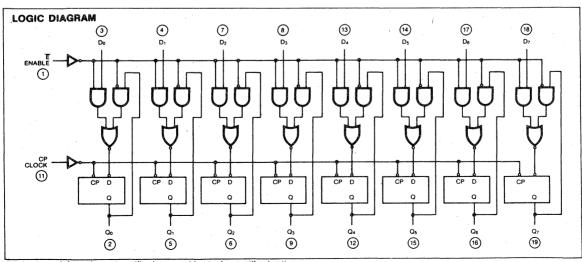

| 54LS/74LS164     | 8-Bit Shift Register (Serial-In Parallel-Out)        |         |

| 54LS/74LS165     | 8-Bit Shift Register (Parallel-In Serial-Out)        |         |

| 3423//428103     | O Dit Office (10gistor (1 didnor in Dorial O de (1   |         |

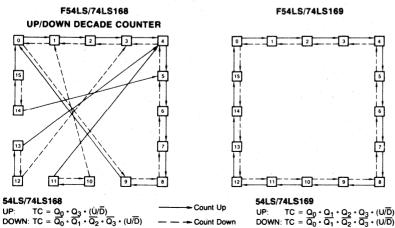

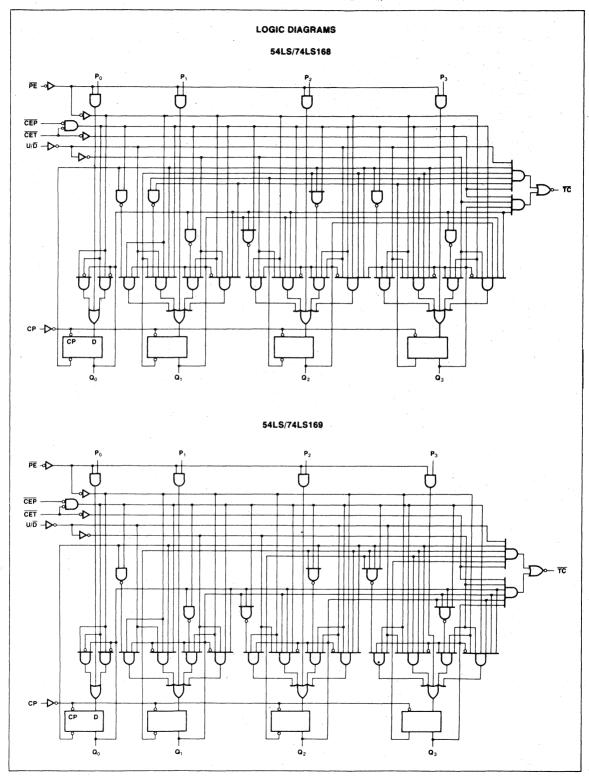

| 54LS/74LS168     | Up/Down Decade Counter                               | 4-128   |

| 54LS/74LS169     | Up/Down Binary Counter                               |         |

|                  | A v A Bogistor File (Open Collector)                 |         |

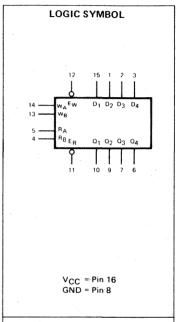

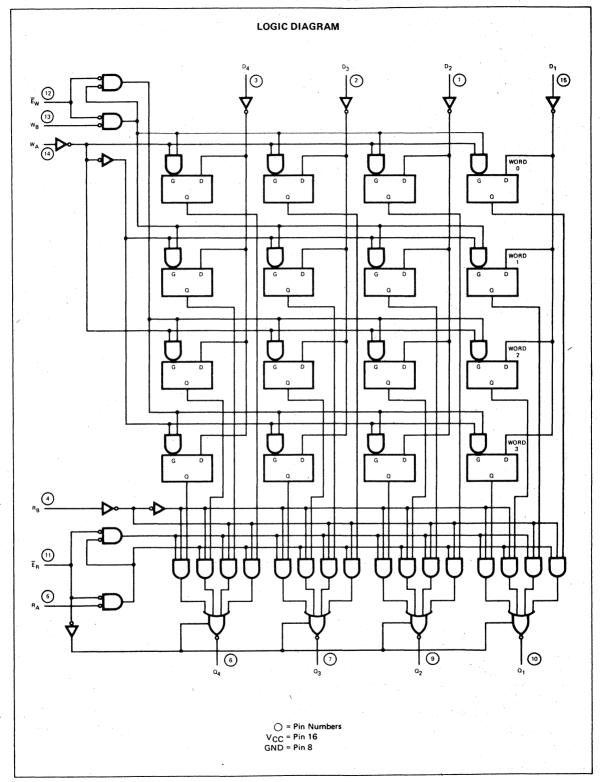

| 54LS/74LS170     | 4 x 4 Register File (Open Collector)                 | 4-138   |

| 54LS/74LS173     | 4-Bit D-Type Register (3-State)                      |         |

| 54LS/74LS174     | Hex D-Type Flip-Flop with Clear                      | 4-142   |

| 54LS/74LS175     | Quad D-Type Flip-Flop with Clear                     | 4-145   |

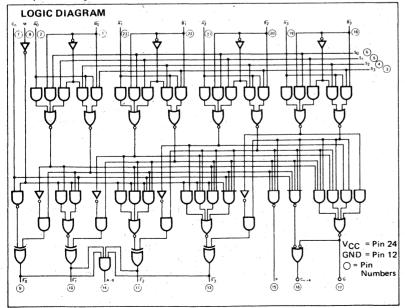

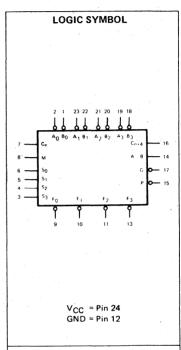

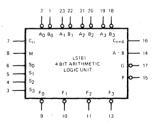

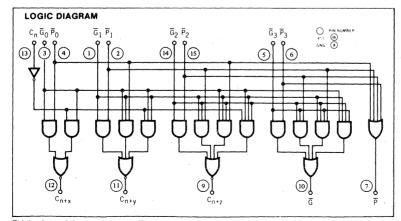

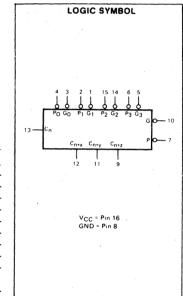

|                  | 4-Bit ALU                                            |         |

| 54LS/74LS181     |                                                      |         |

| 54LS/74LS182     | Carry Lookahead Generator                            |         |

| 54LS/74LS189     | 16 x 4 RAM                                           |         |

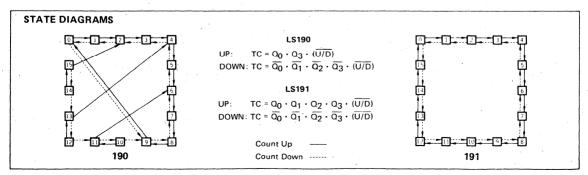

| 54LS/74LS190     | Up/Down Decade Counter                               | 4-150   |

| EALC/741 C101    | Up/Down Binary Counter                               | 4-158   |

| 54LS/74LS191     |                                                      |         |

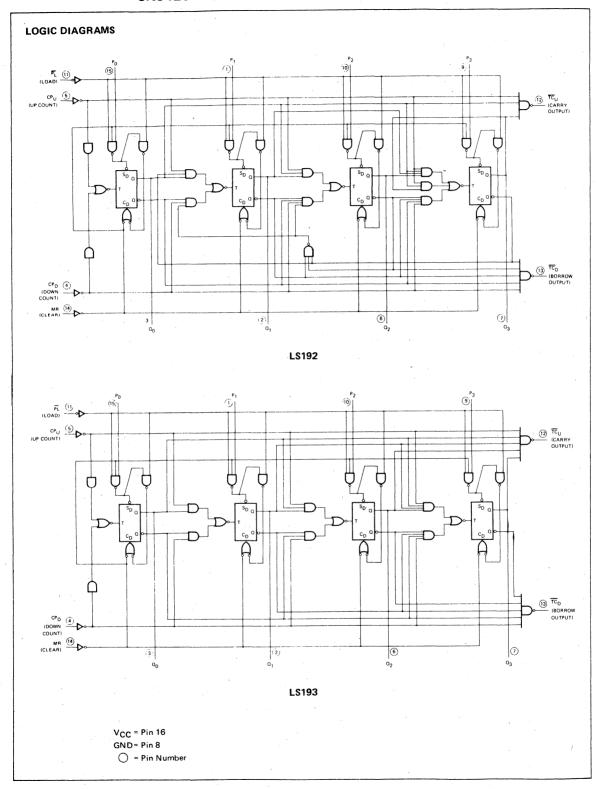

| 54LS/74LS192     | Up/Down Decade Counter                               |         |

| 54LS/74LS193     | Up/Down Binary Counter                               |         |

| 54LS/74LS194A    | 4-Bit Right/Left Shift Register                      |         |

| 54LS/74LS195A    | 4-Bit Shift Register (9300 Type)                     | 4-1/5   |

| 54LS/74LS196     | Decade Counter                                       | 4-179   |

| 54LS/74LS197     | 4-Bit Binary Counter                                 |         |

| 54LS/74LS221     | Dual Monostable Multivibrators                       |         |

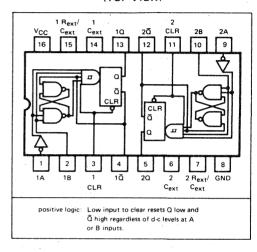

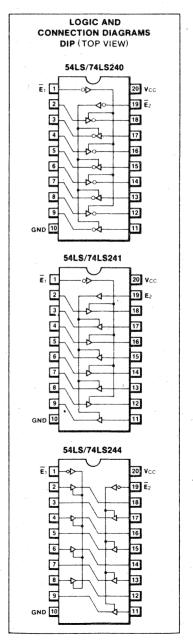

| 54LS/74LS240     | Octal Inverting Bus/Line Driver                      |         |

|                  | Octal Bus Line Driver                                |         |

| 54LS/74LS241     | Octal bus Line Driver                                | . 4-100 |

| 54LS/74LS242     | Quad Bus Transceiver (Inverting)                     | 4-190   |

| 54LS/74LS242     | Quad Bus Transceiver (Non-inverting)                 |         |

| 54LS/74LS244     | Octal 3-State Driver (Non-inverting)                 |         |

|                  | Octal 3-State Driver (Non-inverting)                 |         |

| 54LS/74LS245     |                                                      |         |

| 54LS/74LS247     | BCD to 7-Segment Decoder/Driver (Open Collector)     | . 4-194 |

| 54LS/74LS248     | BCD to 7-Segment Decoder/Driver                      | 4.10/   |

|                  | BCD to 7-Segment Decoder/Driver (Open Collector)     | 4 104   |

| 54LS/74LS249     |                                                      |         |

| 54LS/74LS251     | 8-Input Multiplexer (3-State)                        | 4 100   |

| 54LS/74LS253     | Dual 4-Input Multiplexer (3-State)                   | 4-195   |

| 54LS/74LS256     | Dual 4-Bit Addressable Latch                         | . 4-202 |

### NUMERICAL INDEX OF DEVICES (Cont'd)

| Device         | Description                                   | Page    |

|----------------|-----------------------------------------------|---------|

| 54LS/74LS257A  | Quad 2-Input Multiplexer (3-State)            | . 4-206 |

| 54LS/74LS258A  | Quad 2-Input Multiplexer (3-State)            | . 4-209 |

| 54LS/74LS259   | 8-Bit Addressable Latch (9334)                | . 4-212 |

| 54LS/74LS260   | Dual 5-Input NOR Gate                         |         |

| 54LS/74LS266   | Quad Exclusive NOR (Open Collector)           | . 4-217 |

|                |                                               |         |

| 54LS/74LS273   | Octal D-Type Flip-Flop with Master Reset      |         |

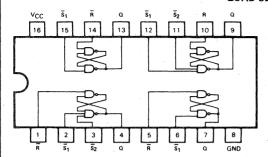

| 54LS/74LS279   | Quad Set-Reset Latch                          |         |

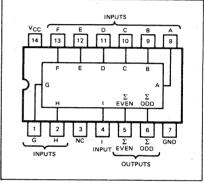

| 54LS/74LS280   | 9-Bit Odd/Even Parity Generators/Checkers     | . 4-222 |

| 54LS/74LS283   | 4-Bit Full Adder (Rotated LS83)               |         |

| 54LS/74LS289   | 16 x 4 RAM (Open Collector)                   | . 4-226 |

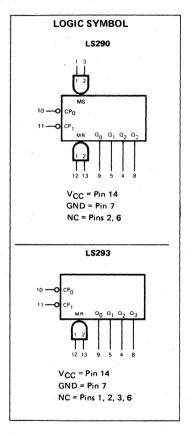

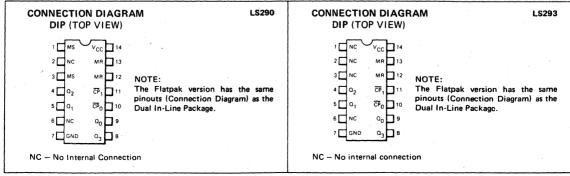

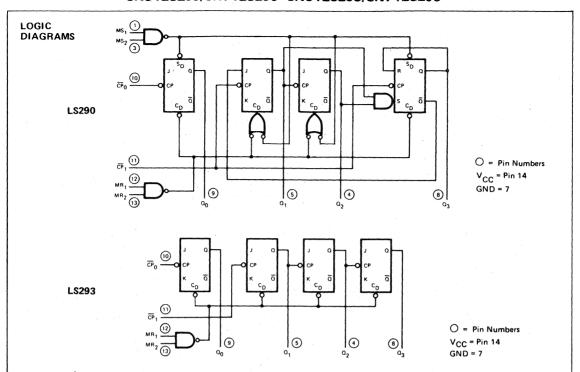

| 54LS/74LS290   | Decade Counter                                | 4.227   |

| 54LS/74LS293   | 4-Binary Counter.                             |         |

| 54LS/74LS295A  | 4-Bit Shift Register (3-State)                |         |

|                |                                               |         |

| 54LS/74LS298   | Quad 2-Input Multiplexer with Output Latches  |         |

| 54LS/74LS299   | 8-Bit Universal Shift Register                | . 4-239 |

| 54LS/74LS322   | 8-Bit Shift Registers with Sign Extend        | . 4-243 |

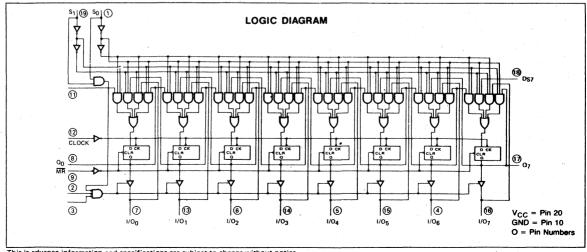

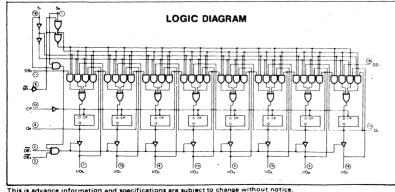

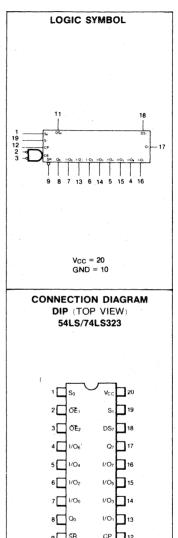

| 54LS/74LS323   | 8-Bit Universal Shift/Storage Register        |         |

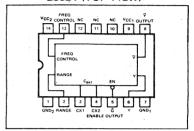

| 54LS/74LS324   | Voltage-Controlled Oscillators                |         |

| 54LS/74LS325   | Voltage-Controlled Oscillators                |         |

| 54LS/74LS326   | Voltage-Controlled Oscillators                |         |

| 0120,7120020   |                                               |         |

| 54LS/74LS327   | Voltage-Controlled Oscillators                | . 4-247 |

| 54LS/74LS352   | 4-Input Multiplexer                           | . 4-248 |

| 54LS/74LS353   | Dual 4-Input Multiplexer (3-State LS352)      | . 4-251 |

| 54LS/74LS365A  | Hex Buffer with Common Enable (3-State)       |         |

| 54LS/74LS366A  | Hex Inverter with Common Enable (3-State)     | . 4-255 |

|                |                                               |         |

| 54LS/74LS367A  | Hex Buffer, 4-Bit and 2-Bit (3-State)         | . 4-255 |

| 54LS/74LS368A  | Hex Inverter, 4-Bit and 2-Bit (3-State)       |         |

| 54LS/74LS373   | Octal Transparent Latch                       |         |

| 54LS/74LS374   | Octal D-Type Flip-Flop                        |         |

| 54LS/74LS375   | Quad Latch                                    |         |

| 5.1.0/3.1.0033 |                                               |         |

| 54LS/74LS377   | Octal D-Type Flip-Flop with Enable            |         |

| 54LS/74LS378   | Hex D-Type Flip-Flop with Enable              |         |

| 54LS/74LS379   | 4-Bit D-Type Flip-Flop with Enable            |         |

| 54 LS/74 LS384 | 8-Bit By 1-Bit Two's-Complement Multipliers   | . 4-273 |

| 54LS/74LS385   | Quadruple Serial Adders/Subtractors           | . 4-274 |

| 54LS/74LS386   | Quad Exclusive OR Gate                        | 4-275   |

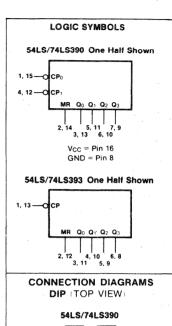

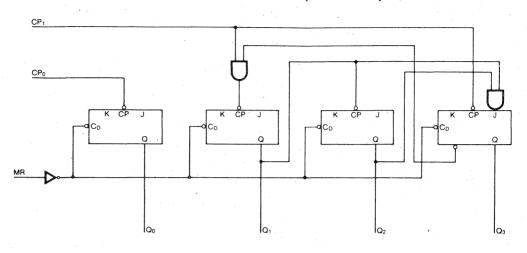

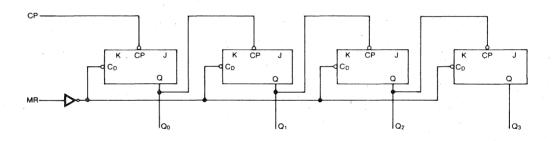

| 54LS/74LS390   | Dual Decade Counter                           |         |

| 54LS/74LS393   | Dual 4-Bit Binary Counter                     |         |

| 54LS/74LS395   | 4-Bit Shift Register (3-State)                |         |

|                |                                               |         |

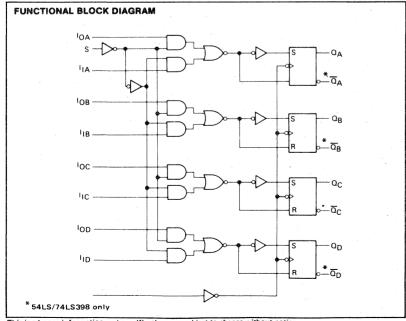

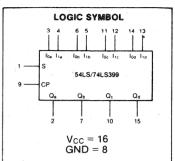

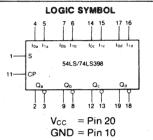

| 54LS/74LS398   | Quad 2-Input Multiplexer with Output Register | 4-204   |

| 54LS/74LS399   | Quad 2-Input Multiplexer with Output Register | 4-284   |

| 54LS/74LS490   | Dual Decade Counter                           | . 4-288 |

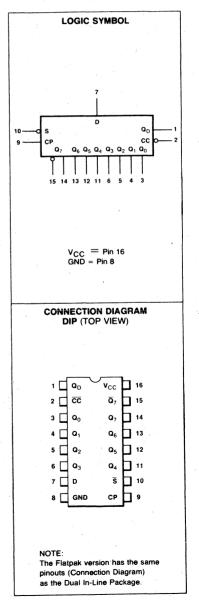

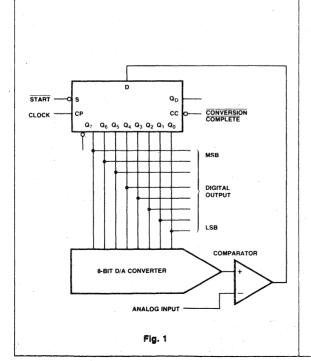

| 54LS/74LS502   | 8-Bit Successive Approximation Register       | . 4-291 |

| 54LS/74LS540   | Octal Inverting Bus/Line Driver               | . 4-294 |

| 54LS/74LS541   | Octal Bus/Line Driver                         | . 4-294 |

| 54LS/74LS568   | Decade Up/Down Counter (3-State)              | 4-297   |

| 54LS/74LS569   | Binary Up/Down Counter (3-State)              | 4.207   |

| 54LS/74LS573   | Octal Transparent Latch (3-State)             |         |

| 54LS/74LS573   |                                               |         |

|                | Octal D-Type Flip-Flop (3-State)              |         |

| 54LS/74LS640   | Octal Bus Transceivers with 3-State Outputs   | . 4-301 |

| 54LS/74LS641   | Octal Bus Transceivers with 3-State Outputs   | 4-301   |

| 54LS/74LS642   | Octal Bus Transceivers with 3-State Outputs   |         |

| 54LS/74LS645   | Octal Bus Transceivers with 3-State Outputs   | . 4-301 |

| 54LS/74LS670   | 4 x 4 Register File (3-State)                 |         |

# **Circuit Characteristics**

### **LOW POWER SCHOTTKY**

### CIRCUIT CHARACTERISTICS

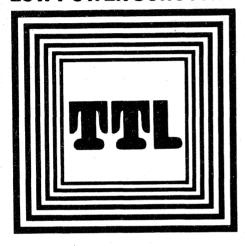

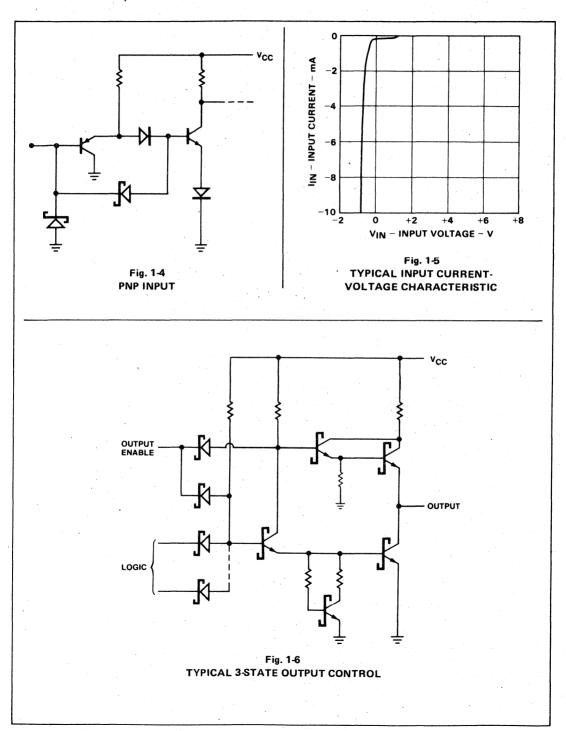

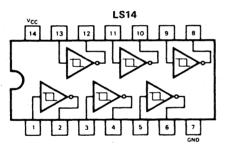

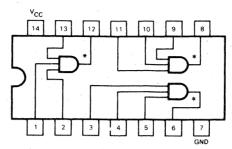

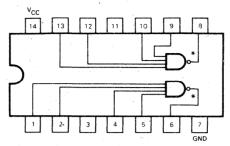

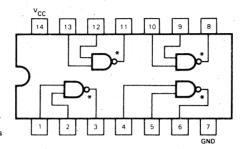

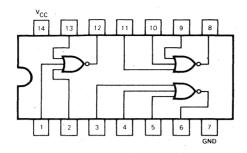

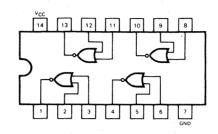

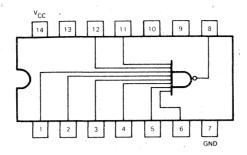

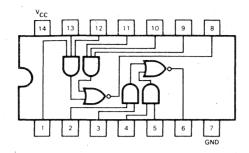

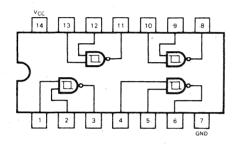

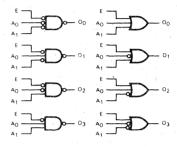

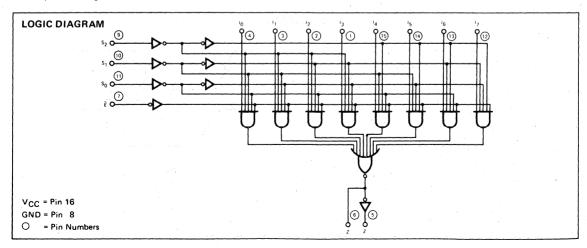

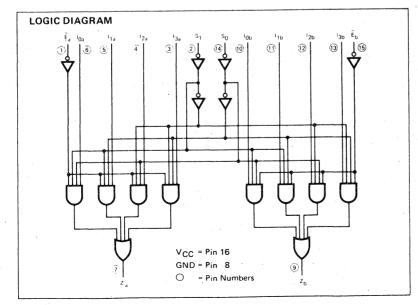

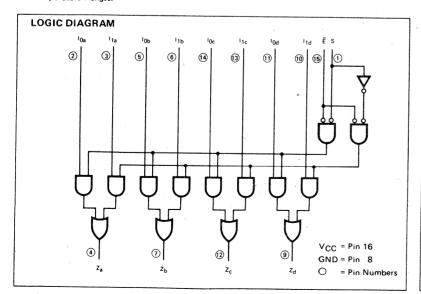

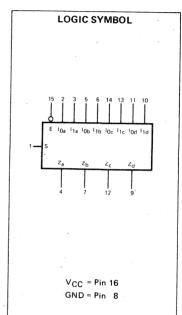

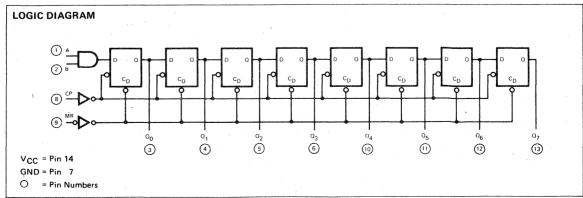

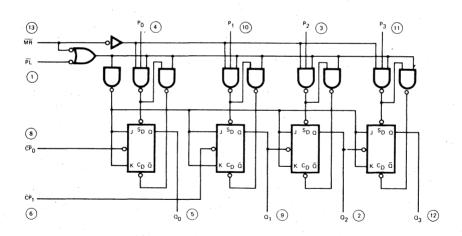

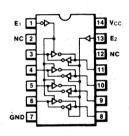

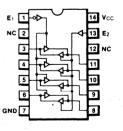

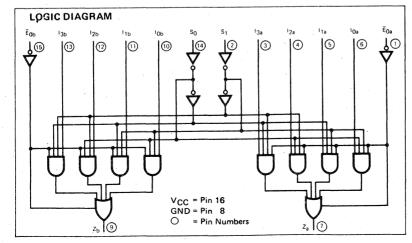

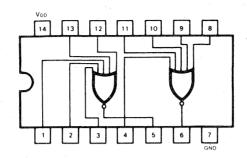

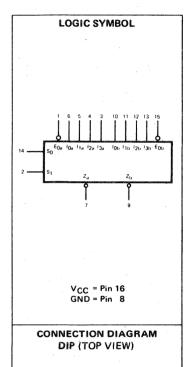

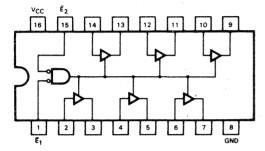

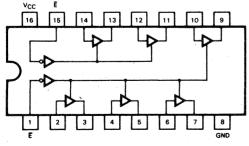

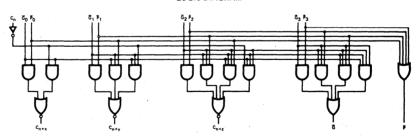

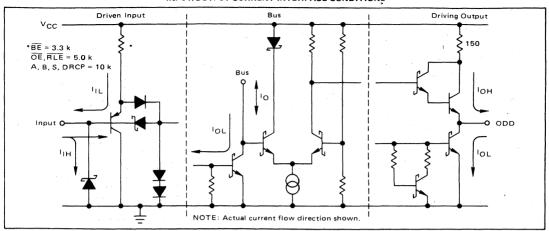

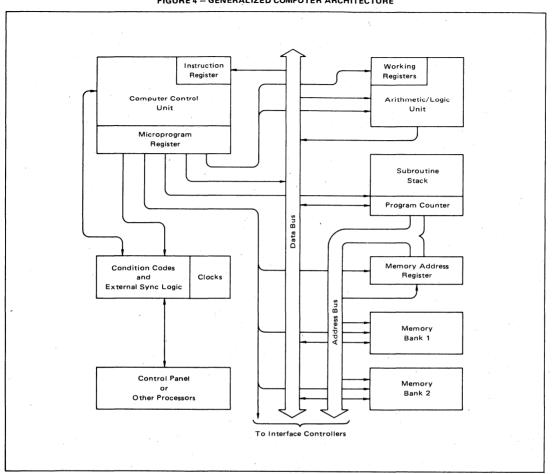

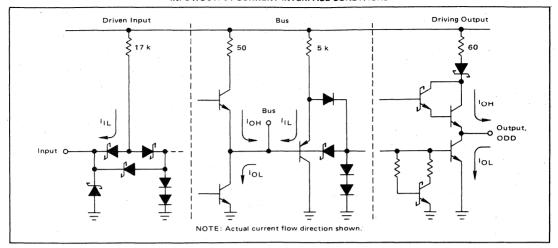

LSTTL circuit features are best understood by examining the LS002-input NAND gate (Figure 1-1). The input/output circuits of all LSTTL are almost identical. Although the logic function and basic structure of LS circuits are the same as conventional TTL, there are also significant differences.

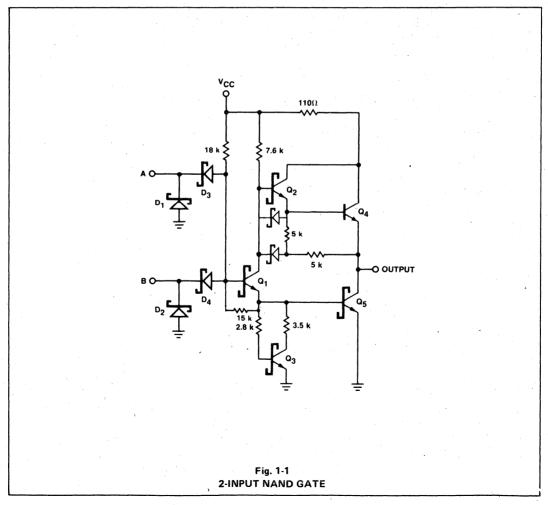

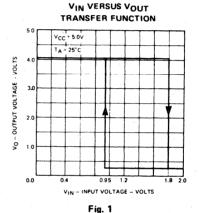

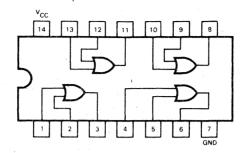

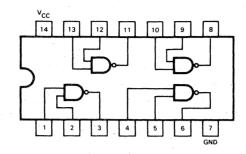

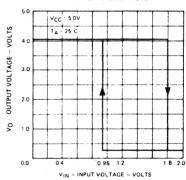

**INPUT CONFIGURATION.** With a few exceptions, LSTTL circuits do not use the multi-emitter input structure that originally gave TTL its name. Most LS elements use a DTL type input circuit with Schottky diodes to perform the AND function, as exemplified by D3 and D4 in *Figure 1-1*. Compared to the classical multi-emitter structure, this circuit is faster and it increases the input breakdown voltage. Inputs of this type are tested for leakage with an applied input voltage of 10 V and the input breakdown voltage is typically 15 V or more. *Figure 1-2* shows the Vout/VIN transfer function of an LS00 gate. The input threshold is approximately 0.1 V lower than for standard TTL.

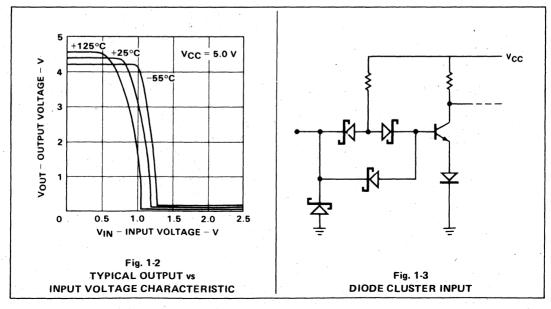

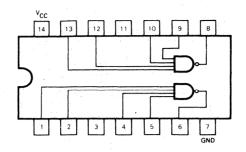

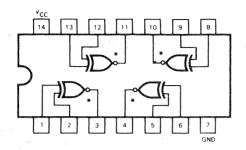

Another input arrangement often used in MSI has three diodes connected as shown in *Figure 1-3*. This configuration gives a slightly higher input threshold than that of *Figure 1-1*.

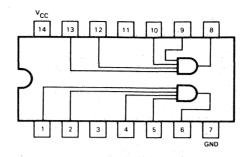

A third input configuration that is sometimes used employs a vertical PNP transistor as shown in *Figure 1-4*. This arrangement also gives a higher input threshold and has the additional advantage of reducing the amount of current that the signal source must sink. Both the diode cluster arrangement and the PNP input configuration have breakdown voltage ratings greater than 10 V.

All inputs are provided with clamping diodes, exemplified by D1 and D2 in *Figure 1-1*. These diodes conduct when an input signal goes negative (*Figure 1-5*), which limits undershoot and helps to control ringing on long signal lines following a HIGH-to-LOW transition. These diodes are intended only for the suppression of transient currents and should not be used as steady-state clamps in interface applications. A clamp current exceeding 2 mA and with a duration greater than 500 ns can activate a parasitic lateral NPN transistor, which in turn can steal current from internal nodes of the LS circuit and thus cause logic errors.

The effective capacitance of an LSTTL input is 5 pF for DIP and 4 pF for Flatpak. For an input that serves more than one internal function, each additional function adds 1.5 pF.

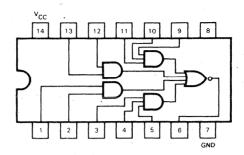

**OUTPUT CONFIGURATION.** The output circuitry of LSTTL have several features not found in conventional TTL. A few of these features are discussed below.

Referring to Figure 1-1, the base of the pull-down output transistor Q5 is returned to ground through Q3 and a pair of resistors instead of through a simple resistor. This arrangement is called a squaring network since it squares up the transfer characteristics (Figure 1-2) by preventing conduction in the phase splitter Q1 until the input voltage rises high enough to allow Q1 to supply base current to Q5. The squaring network also improves the propagation delay by providing a low resistance path to discharge capacitance at the base of Q5 during turn-off.

The output pull-up circuit is a 2-transistor Darlington circuit with the base of the output transistor returned through a 5 K resistor to the output terminals, unlike 74H and 74S where it is returned to ground which is a more power consuming configuration. This configuration allows the output to pull up to one  $V_{BE}$  below  $V_{CC}$  for low values of output current.

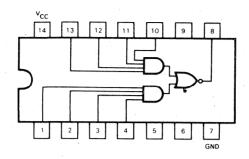

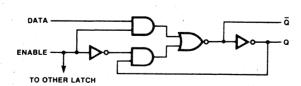

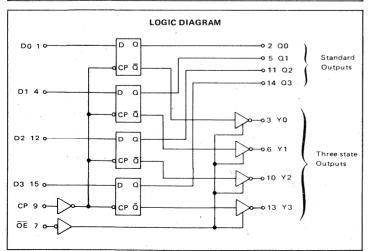

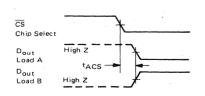

Figure 1-6 shows the extra circuitry used to obtain the "high Z" condition in 3-state outputs. When the Output Enable signal is LOW, both the phase splitter and the Darlington pull-up are turned off. In this condition the output circuitry is non-conducting, which allows the outputs of 2 or more such circuits to be connected together in a bus application wherein only one output is enabled at any particular time.

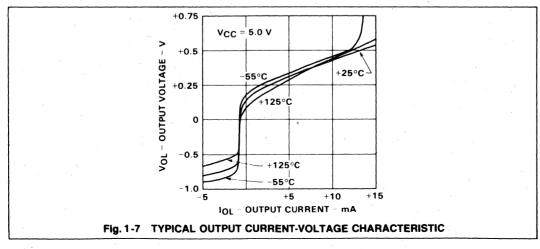

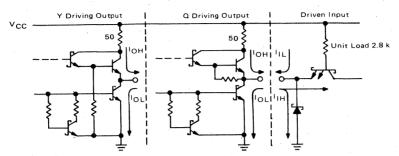

**OUTPUT CHARACTERISTICS.** Figure 1-7 shows the LOW-state output characteristics. For LOW I<sub>OL</sub> values, the pull-down transistor is clamped out of deep saturation to shorten the turn-off delay. The curves also show the clamping effect when I<sub>OL</sub> tends to go negative, as it often does due to reflections on a long interconnection after a negative-going transition. This clamping effect helps to minimize ringing.

The waveform of a rising output signal resembles an exponential, except that the signal is slightly rounded at the beginning of the rise. Once past this initial rounded portion, the starting-edge rate is approximately 0.5 V/ns with a 15 pF load and 0.25 V/ns with a 50 pF load. For analytical purposes, the rising waveform can be approximated by the following expression.

$$V(t) = V_{OL} + 3.7 \left[ 1 - exp \left( -t/T \right) \right]$$

where

$$T = 8 \text{ ns for } C_L = 15 \text{ pF and 16 ns for } C_L = 50 \text{ pF}$$

The waveform of a falling output signal resembles that part of a cosine wave between angles of 0° and 180°. Fall times from 90% to 10% are approximately 4.5 ns with a 15 pF load and 8.5 ns with a 50 pF load. Equivalent edge rates are approximately 0.8 and 0.4 V/ns respectively. For analytical purposes, the falling waveform can be approximated by the following.

$$V(t) = V_{OL} + 1.9 \ \mu(t) \left[ 1 + \cos \omega t \right] - 1.9 \ \mu(t-a) \left[ 1 + \cos \omega (t-a) \right]$$

where  $\mu(t) = 0$  for  $t < 0$  and  $\mu(t-a) = 0$  for  $t < a$

$= 1$  for  $t > a$

For t in nanoseconds and  $C_L$  = 15 pF, a = 7.5 ns,  $\omega$  = 0.42

For

$$C_L = 50$$

pF,  $a = 14$  ns,  $\omega = 0..23$

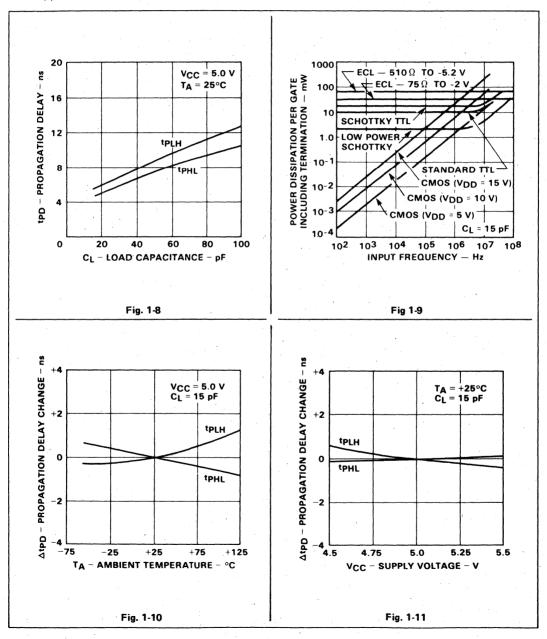

**AC SWITCHING CHARACTERISTICS.** The average propagation delay of a Low Power Schottky gate is 5 ns at a load of 15 pF as shown in *Figure 1-8*. The delay times increase at an average of 0.08 ns/pF for larger values of capacitance load. These delay times are relatively insensitive to variations in power supply and temperature. The average propagation delay time changes less than 1.0 ns over temperature and less than 0.5 ns with V<sub>CC</sub> for the military temperature and voltage ranges. (See *Figures 1-10* and 1-11).

The power versus frequency characteristics of Motorola's LS family, as shown in *Figure 1-9*, indicate that at operating frequencies above 1 MHz the Low Power Schottky devices are more efficient than CMOS for most applications.

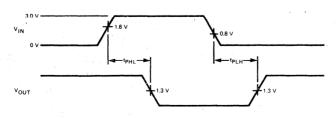

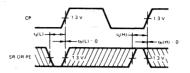

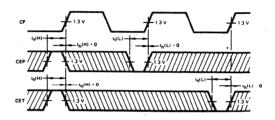

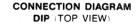

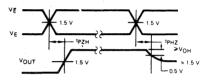

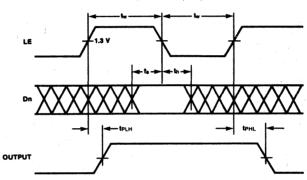

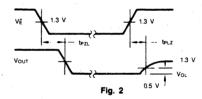

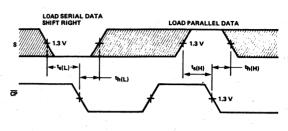

### **AC WAVEFORMS**

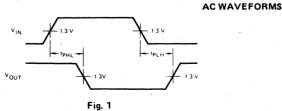

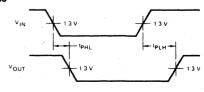

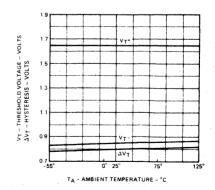

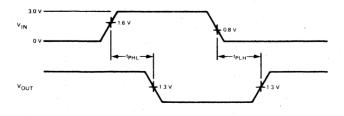

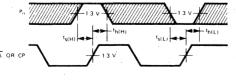

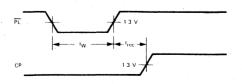

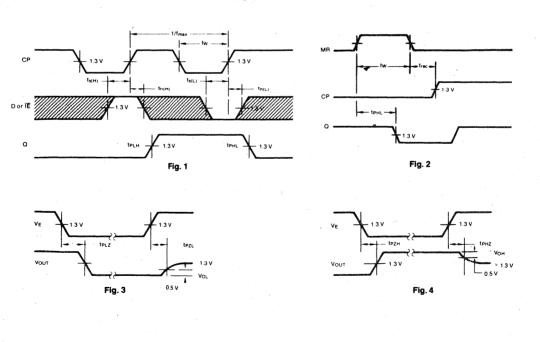

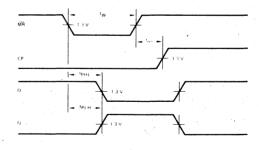

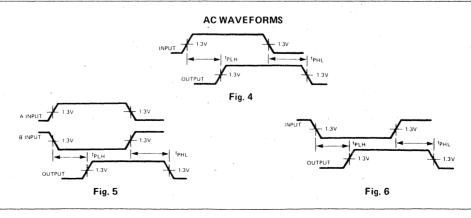

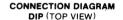

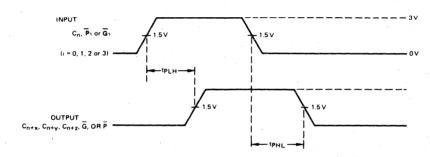

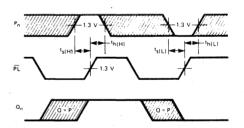

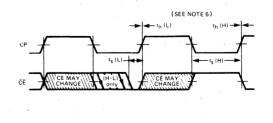

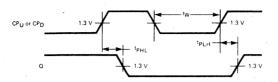

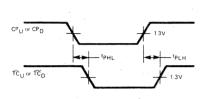

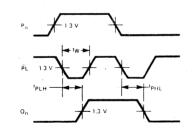

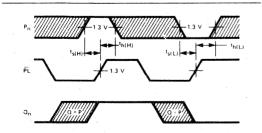

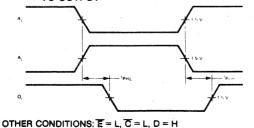

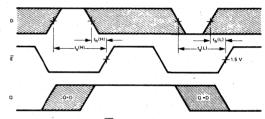

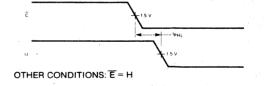

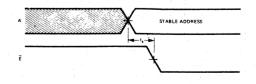

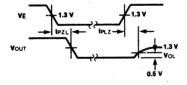

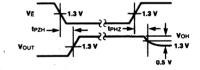

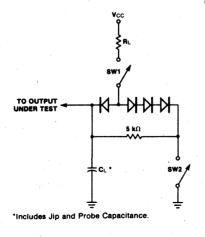

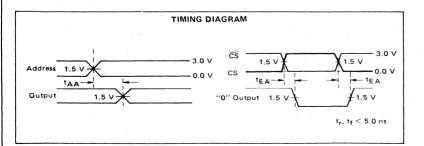

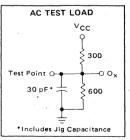

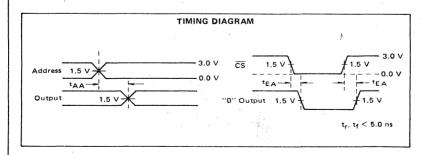

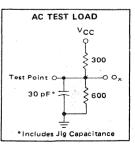

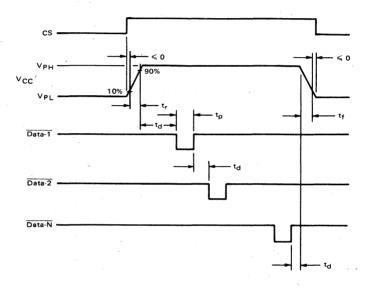

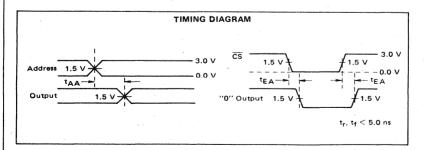

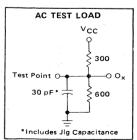

### AC TEST CIRCUITS AND WAVEFORMS

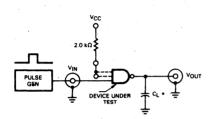

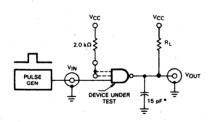

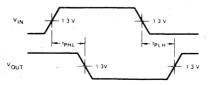

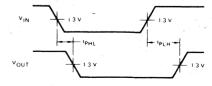

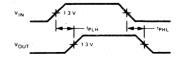

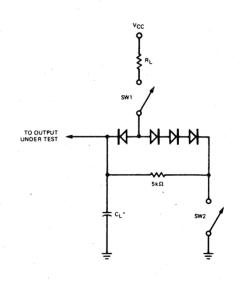

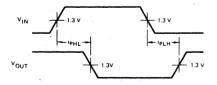

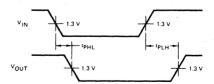

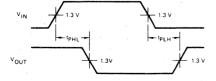

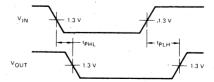

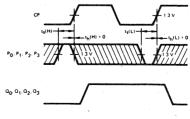

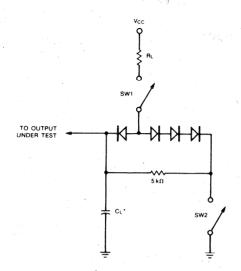

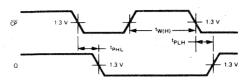

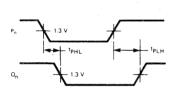

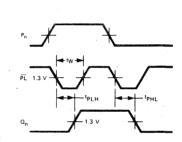

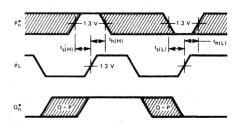

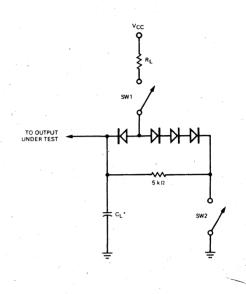

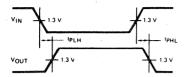

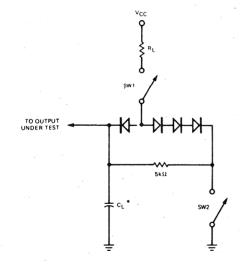

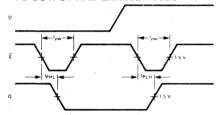

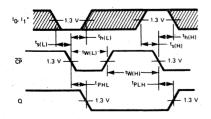

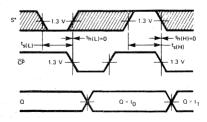

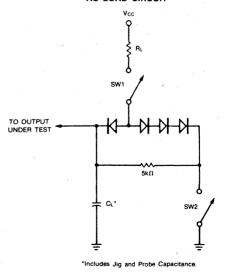

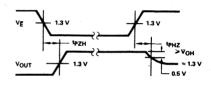

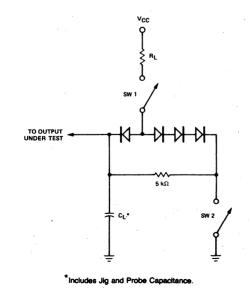

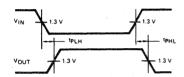

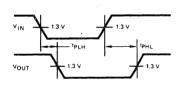

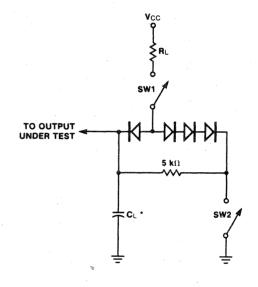

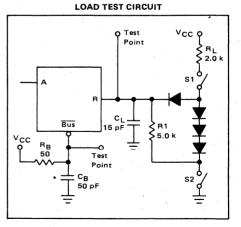

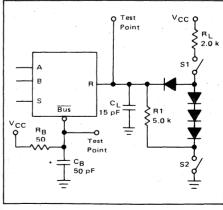

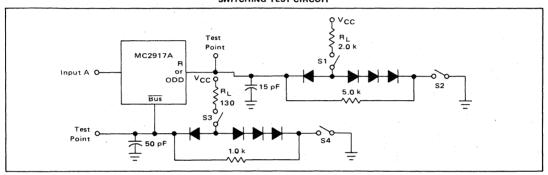

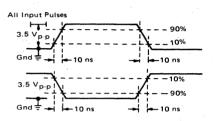

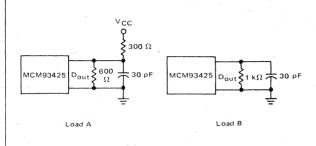

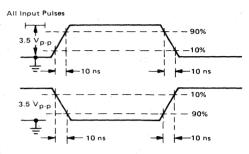

The following test circuits and conditions represent Motorola's typical AC test procedures. The output loading for standard Low Power Schottky devices is a 15 pF capacitor. Experimental evidence shows that test results using the additional diode-resistor load are within 0.2 ns of the capacitor only load. The capacitor only load also has the advantage of repeatable, easily correlated test results. The input pulse rise and fall times are specified at 6 ns to closely approximate the Low Power Schottky output transitions through the active threshold region. The specified propagation delay limits can be guaranteed with a 15 ns input rise time on all parameters except those requiring narrow pulse widths. Any frequency measurement over 15 MHz or pulse width less than 30 ns must be performed with a 6 ns input rise time.

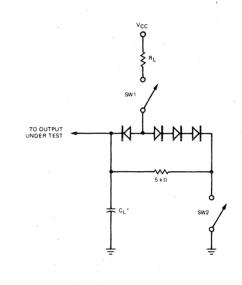

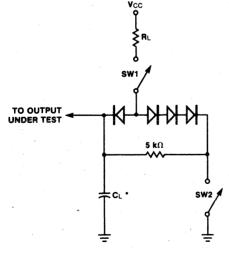

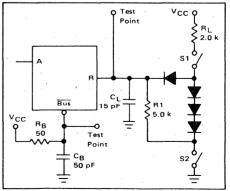

#### **Test Circuit for Standard Output Devices**

\*Includes all probe and jig capacitance

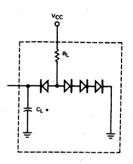

### Optional Load (Guaranteed-Not Tested)

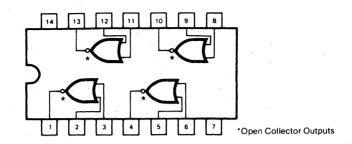

### **Test Circuit for Open Collector Output Devices**

\*Includes all probe and jig capacitance

# Pulse Generator Settings (unless otherwise specified)

Frequency = 1 MHz Duty Cycle = 50%  $t_{TLH}(t_r) = 6 \text{ ns}$  $t_{THL}(t_f) = 6 \text{ ns}$ Amplitude = 0 to 3 V

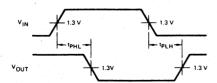

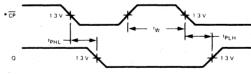

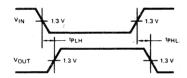

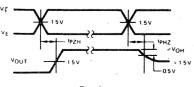

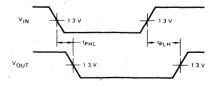

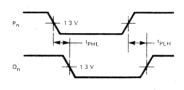

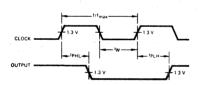

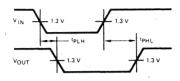

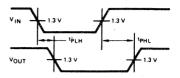

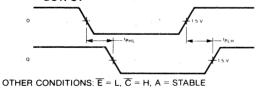

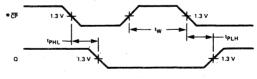

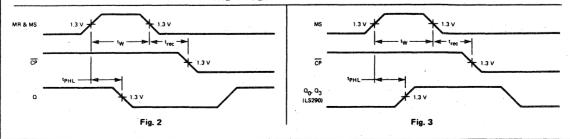

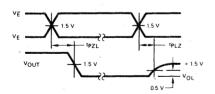

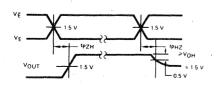

#### **Waveform for Inverting Outputs**

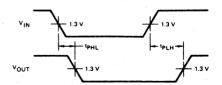

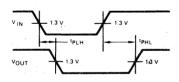

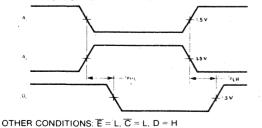

### **Waveform for Non-inverting Outputs**

### **ABSOLUTE MAXIMUM RATINGS**

(above which the useful life may be impaired)

Storage Temperature

Temperature (Ambient) Under Bias

Vcc Pin Potential to Ground Pin

\*Input Voltage (dc) Diode Inputs

\*Input Current (dc)

\*Input Voltage (dc) Emitter Inputs

Voltage Applied to Outputs (Output HIGH)

High Level Voltage Applied to Disabled 3-State Output

-65°C to +150°C -55°C to +125°C -0.5 V to +7.0 V -0.5 V to 15 V -30 mA to +5.0 mA -0.5 V to +5.5 V -0.5 V to +10 V 7.0 V

Device types having inputs limited to 5.5 V are as follows:

SN74LS196, SN74LS197—Emitter inputs on clock terminals.

SN74LS390/393 — Emitter inputs on clock terminals.

SN74LS242/243, SN74LS245—Inputs connected to outputs.

SN74LS640/641/642/645 —Inputs connected to outputs.

<sup>\*</sup>Either input voltage limit or input current limit is sufficient to protect the inputs—Circuits with 5.5V maximum limits are listed below.

# LOW POWER SCHOTTKY

# **Design Considerations**

### **DESIGN CONSIDERATIONS**

**SUPPLY VOLTAGE AND TEMPERATURE RANGE.** The nominal supply voltage ( $V_{CC}$ ) for all TTL circuits is +5.0 V. Commercial grade parts are guaranteed to perform with a  $\pm5\%$  supply tolerance ( $\pm250$  mV) over an ambient temperature range of 0°C to 70°C. MIL-grade parts are guaranteed to perform with a  $\pm10\%$  supply tolerance ( $\pm500$  mV) over an ambient temperature range of -55°C to +125°C.

TTL families may be mixed for optimum system design. The following tables specify the worst case noise immunity in mixed systems.

### Worst Case TTL DC Noise Immunity/Noise Margins

#### **Electrical Characteristics**

|      |        |                                  | Military (-55 to +125°C) |     |     |     | Commercial (0 to 70°C) |     |     |     |       |

|------|--------|----------------------------------|--------------------------|-----|-----|-----|------------------------|-----|-----|-----|-------|

| Item | Symbol | TTL Families                     | V <sub>IL</sub>          | VIH | VOL | VOH | VIL                    | VIH | VOL | VOH | Units |

| . 6  | TTL    | Standard TTL 9000, 54/74         | 0.8                      | 2.0 | 0.4 | 2.4 | 0.8                    | 2.0 | 0.4 | 2.4 | ٧     |

| 7    | HTTL   | High Speed TTL, 54H/74H          | 0.8                      | 2.0 | 0.4 | 2.4 | 0.8                    | 2.0 | 0.4 | 2.4 | V     |

| 8    | LPTTL  | Low Power TTL, 93L00 (MSI)       | 0.7                      | 2.0 | 0.3 | 2.4 | 0.8                    | 2.0 | 0.3 | 2.4 | V     |

| 9    | STTL   | Schottky TTL 54S/74S, 93S00      | 0.8                      | 2.0 | 0.5 | 2.5 | 0.8                    | 2.0 | 0.5 | 2.7 | V     |

| 10   | LSTTL  | Low Power Schottky TTL 54LS/74LS | 0.7                      | 2.0 | 0.4 | 2.5 | 0.8                    | 2.0 | 0.5 | 2.7 | V     |

$V_{OL}$  and  $V_{OH}$  are the voltages generated at the output.  $V_{IL}$  and  $V_{IH}$  are the voltage required at the input to generate the appropriate levels. The numbers given above are guaranteed worst-case values.

#### LOW Level Noise Margins (Military)

| From  | TTL | HTTL | LPTTL | STTL | LSTTL | Units |

|-------|-----|------|-------|------|-------|-------|

| TTL   | 400 | 400  | 300   | 400  | 300   | mV    |

| HTTL  | 400 | 400  | 300   | 400  | 300   | mV    |

| LPTTL | 500 | 500  | 400   | 500  | 400   | mV    |

| STTL  | 300 | 300  | 200   | 300  | 200   | ∞mV   |

| LSTTL | 400 | 400  | 300   | 400  | 300   | mV    |

From "VOL" to "VIL"

#### HIGH Level Noise Margins (Military)

| From To | TTL | HTTL  | LPTTL | STTL | LSTTL | Units |

|---------|-----|-------|-------|------|-------|-------|

| TTL     | 400 | 400   | 400   | 400  | 400   | mV    |

| HTTL    | 400 | 400   | 400   | 400  | 400   | mV    |

| LPTTL   | 400 | 400   | 400   | 400  | 400   | mV    |

| STTL    | 500 | 500   | 500   | 500  | 500   | mV    |

| LSTTL   | 500 | 500 ′ | 500   | 500  | 500   | mV    |

From "VOH" to "VIH"

#### LOW Level Noise Margins (Commercial)

| From  | TTL  | HTTL | LPTTL | STTL | LSTTL | Units |

|-------|------|------|-------|------|-------|-------|

| TTL · | 400  | 400  | 400   | 400  | 400   | mV    |

| HTTL  | 400  | 400  | 400   | 400  | 400   | m۷    |

| LPTTL | -500 | 500  | 500   | 500  | 500   | mV    |

| STTL  | 300  | 300  | 300   | 300  | 300   | mV    |

| LSTTL | 300  | 300  | 300   | 300  | 300   | mV    |

From "VOL" to VIL"

### HIGH Level Noise Margins (Commercial)

| From  | TTL | HTTL | LPTTL | STTL | LSTTL | Units |

|-------|-----|------|-------|------|-------|-------|

| TTL   | 400 | 400  | 400   | 400  | 400   | mV    |

| HTTL  | 400 | 400  | 400   | 400  | 400   | m۷    |

| LPTTL | 400 | 400  | 400   | 400  | 400   | mV    |

| STTL  | 700 | 700  | 700   | 700  | 700   | mV    |

| LSTTL | 700 | 700  | 700   | 700  | 700   | mV    |

From "VOH" to "VIH"

FAN-IN AND FAN-OUT. In order to simplify designing with Motorola TTL devices, the input and output loading parameters of all families are normalized to the following values:

1 TTL Unit Load (U.L.) = 40

$$\mu$$

A in the HIGH state (logic "1")

Input loading and output drive factors of all products described in this handbook are related to these definitions.

### **EXAMPLES - INPUT LOAD**

- 1. A 7400 gate, which has a maximum  $I_{IL}$  of 1.6 mA and  $I_{IH}$  of 40  $\mu$ A is specified as having an input load factor of 1 U.L. (Also called a fan-in of 1 load.)

- 2. The 74LS95B which has a value of  $I_{IL}=0.8$  mA and  $I_{IH}$  of 40  $\mu$ A on the CP terminal, is specified as having an input LOW load factor of

$$\frac{0.8 \text{ mA}}{1.6 \text{ mA}}$$

or 0.5 U.L.

and an input HIGH load factor of

$$\frac{40 \mu A}{40 \mu A}$$

or 1 U.L.

3. The 74LS00 gate which has an  $I_{IL}$  of 0.36 mA and an  $I_{IH}$  of 20  $\mu$ A, has an input LOW load factor of

(normally rounded to 0.25 U.L.) and an input HIGH load factor of

$$\frac{20 \mu A}{40 \mu A}$$

or 0.5 U.L.

#### **EXAMPLES - OUTPUT DRIVE**

1. The output of the 7400 will sink 16 mA in the LOW (logic "0") state and source 800  $\mu$ A in the HIGH (logic "1") state. The normalized output LOW drive factor is therefore

$$\frac{16 \text{ mA}}{1.6 \text{ mA}} = 10 \text{ U.L.}$$

and the output HIGH drive factor is

$$\frac{800 \mu A}{40 \mu A}$$

or 20 U.L.

2. The output of the 74LS00 will sink 8.0 mA in the LOW state and source 400  $\mu$ A in the HIGH state. The normalized output LOW drive factor is

$$\frac{8.0 \text{ mA}}{1.6 \text{ mA}}$$

or 5 U.L.

and the output HIGH drive factor is

$$\frac{400 \mu A}{40 \mu A}$$

or 10 U.L.

Relative load and drive factors for the basic TTL families are given in Table 1.

TABLE I

|        | INPUT     | LOAD      | OUTPUT DRIVE |           |  |

|--------|-----------|-----------|--------------|-----------|--|

| FAMILY | HIGH      | LOW       | HIGH         | LOW       |  |

| 74LS00 | 0.5 U.L.  | 0.25 U.L. | 10 U.L.      | 5 U.L.    |  |

| 7400   | 1 U.L.    | 1 U.L.    | 20 U.L.      | 10 U.L.   |  |

| 9000   | 1 U.L.    | 1 U.L.    | 20 U.L.      | 10 U.L.   |  |

| 74H00  | 1.25 U.L. | 1.25 U.L. | 25 U.L.      | 12.5 U.L. |  |

| 74S00  | 1.25 U.L. | 1.25 U.L. | 25 U.L.      | 12.5 U.L. |  |

Values for MSI devices vary significantly from one element to another. Consult the appropriate data sheet for actual characteristics.

**WIRED-OR APPLICATIONS.** Certain TTL devices are provided with an "open" collector output to permit the Wired-OR (actually Wired-AND) function. This is achieved by connecting open collector outputs together and adding an external pull-up resistor.

The value of the pull-up resistor is determined by considering the fan-out of the OR tie and the number of devices in the OR tie. The pull-up resistor value is chosen from a range between maximum value (established to maintain the required V<sub>OH</sub> with all the OR tied outputs HIGH) and a minimum value (established so that the OR tie fan-out is not exceeded when only one output is LOW).

# MINIMUM AND MAXIMUM PULL-UP RESISTOR VALUES

$$\begin{split} R_{X(MIN)} &= \frac{V_{CC(MAX)} - V_{OL}}{I_{OL} - N_2(LOW) \bullet 1.6 \, \text{mA}} \\ &\text{where:} \\ \\ R_X &= \text{External Pull-up Resistor} \\ N_1 &= \text{Number of Wired-OR Outputs} \\ N_2 &= \text{Number of Input Unit Loads (U.L.) being Driven} \\ I_{OH} &= I_{CEX} &= \text{Output HIGH Leakage Current} \\ I_{OL} &= \text{LOW Level Fan-out Current of Driving Element} \\ V_{OL} &= \text{Output HIGH Voltage Level (0.5 V)} \\ V_{OH} &= \text{Output HIGH Voltage Level (2.4 V)} \\ V_{CC} &= \text{Power Supply Voltage} \end{split}$$

Example: Four 74LS03 gate outputs driving four other LS gates or MSI inputs.

$$\begin{split} R_{X(MIN)} &= \frac{5.25 \ V - 0.5 V}{8 \ mA - 1.6 \ mA} = \frac{4.75 \ V}{6.4 \ mA} = 742 \ \Omega \\ R_{X(MAX)} &= \frac{4.75 \ V - 2.4 V}{4 \bullet 100 \ \mu A + 2 \bullet 40 \ \mu A} = \frac{2.35 \ V}{0.48 \ mA} = 4.9 \ k\Omega \\ \text{where:} \quad & N_1 &= 4 \\ & N_2(HIGH) &= 4 \bullet 0.5 \ U.L. = 2 \ U.L. \\ & N_2(LOW) &= 4 \bullet 0.25 \ U.L. = 1 \ U.L. \\ & I_{OH} &= 100 \ \mu A \\ & I_{OL} &= 8 \ mA \\ & V_{OL} &= 0.5 \ V \\ & V_{OH} &= 2.4 \ V \end{split}$$

Any value of pull-up resistor between 742  $\Omega$  and 4.9 k $\Omega$  can be used. The lower values yield the fastest speeds while the higher values yield the lowest power dissipation.

**UNUSED INPUTS.** For best noise immunity and switching speed, unused TTL inputs should not be left floating, but should be held between 2.4 V and the absolute maximum input voltage.

Two possible ways of handling unused inputs are:

- Connect unused input to V<sub>CC</sub>. Most LSTTL inputs have a breakdown voltage >15 V and require, therefore, no series resistor. For all multi-emitter conventional TTL inputs, a 1-to-10 kΩ current limiting series resistor is recommended, to protect against V<sub>CC</sub> transients that exceed 5.5 V.

- 2. Connect the unused input to the output of an unused gate that is forced HIGH.

CAUTION: Do not connect an unused LSTTL input to another input of the same NAND or AND function. This method, recommended for normal TTL, increases the input coupling capacitance and thus reduces the ac noise immunity.

**INTERCONNECTION DELAYS.** For those parts of a system in which timing is critical, designers should take into account the finite delay along the interconnections. These range from about 0.12 to 0.15 ns/inch for the type of interconnections normally used in TTL systems. Exceptions occur in systems using ground planes with STTL to reduce ground noise during a logic transition; ground planes give higher distributed capacitance and delays of about 0.15 to 0.22 ns/inch.

Most interconnections on a logic board are short enough that the wiring and load capacitance can be treated as a lumped capacitance for purposes of estimating their effect on the propagation delay of the driving circuit. When an interconnection is long enough that its delay is one-fourth to one-half of the signal transition time, the driver output waveform exhibits noticeable slope changes during a transition. This is evidence that during the initial portion of the output voltage transition the driver sees the characteristic impedance of the interconnection (normally 150  $\Omega$  to 200  $\Omega$ ), which for transient conditions appears as a resistor returned to the quiescent voltage existing just before the beginning of the transition. This characteristic impedance forms a voltage divider with the driver output impedance, tending to produce a signal transition having the same rise or fall time as in the no-load condition but with a reduced amplitude. This attenuated signal travels to the far end of the interconnection, which is essentially an unterminated transmission line, where upon the signal starts doubling. Simultaneously, a reflection voltage is generated which has the same amplitude and polarity as the original signal, e.g., if the driver output signal is positive-going the reflection will be positive-going, and as it travels back toward the driver it adds to the line voltage. At the instant the reflection arrives at the driver it adds algebraically to the still-rising driver output, accelerating the transition rate and producing the noticeable change in slope.

If an interconnection is of such length that its delay is longer than half the signal transition time, the attenuated output of the driver has time to reach substantial completion before the reflection arrives. In the limit, the waveform observed at the driver output is a 2-step signal with a pedestal. In this circumstance the first load circuit to receive a full signal is the one at the far end, because of the doubling effect, while the last one to receive a full signal is the one nearest the driver since it must wait for the reflection to complete the transition. Thus, in a worst-case situation, the net contribution to the overall delay is twice the delay of the interconnection because the initial part of the signal must travel to the far end of the line and the reflection must return.

When load circuits are distributed along an interconnection, the input capacitance of each will cause a small reflection having a polarity opposite that of the signal transition, and each capacitance also slows the transition rate of the signal as it passes by. The series of small reflections, arriving back at the driver, is subtractive and has the effect of reducing the apparent amplitude of the signal. The successive slowing of the transition rate of the transmitted signal means that it takes longer for the signal to rise or fall to the threshold level of any particular load circuit. A rough but workable approach is to treat the load capacitances as an increase in the intrinsic distributed capacitance of the interconnection. Increasing the distributed capacitance of a transmission line reduces its impedance and increases its delay. A good approximation for ordinary TTL interconnections is that distributed load capacitance decreases the characteristic impedance by about one-third and increases the delay by one-half.

Another advantage of LSTTL has to do with its output impedance during a positive-going transition. Whereas the low output impedance of STTL and HTTL allows these circuits to force a larger initial swing into a low impedance interconnection, the low output impedance also has a disadvantage. It makes the reflection coefficient negative at the driven end of the interconnection, a circumstance that exists any time a transmission line is terminated by an impedance lower than its characteristic impadance. This means that when the reflection from the (essentially) open end of the interconnection arrives back at the driver it will be re-reflected with the opposite polarity. The result is a sequence of reflected signals which alternate in sign and decrease in magnitude, commonly known as ringing. The lower the driver output impedance, the greater the amplitude of the ringing and the longer it takes to damp out.

The output impedance of LSTTL, on the other hand, is closer to the characteristic impedance of the interconnections commonly used with TTL, and ringing is practically non-existent. Thus no special packaging is required. This advantage, combined with excellent speed, modest edge rates and very low transient currents, are some of the reasons that designers have found LSTTL extremely easy to work with and very cost effective.

### **DEFINITION OF SYMBOLS AND TERMS USED IN THIS DATABOOK**

**CURRENTS** — Positive current is defined as conventional current flow into a device. Negative current is defined as conventional current flow out of a device. All current limits are specified as absolute values.

- Supply current The current flowing into the V<sub>CC</sub> supply terminal of a circuit with the specified input conditions and the outputs open. When not specified, input conditions are chosen to guarantee worst case operation.

- I<sub>IH</sub> Input HIGH current The current flowing into an input when a specified HIGH voltage is applied.

- I<sub>1L</sub> Input LOW current The current flowing out of an input when a specified LOW voltage is applied.

**DEFINITION OF SYMBOLS AND TERMS USED IN THIS DATABOOK (Cont'd)** l<sub>OH</sub> Output HIGH current - The leakage current flowing into a turned off open collector output with a specified HIGH output voltage applied. For devices with a pull-up circuit, the low is the current flowing out of an output which is in the HIGH state. Output LOW current - The current flowing into an output which is in the LOW loL state. Output short-circuit current - The current flowing out of an output which is in los the HIGH state when that output is short circuit to ground (or other specified potential). loz H Output off current HIGH - The current flowing into a disabled 3-state output with a specified HIGH output voltage applied. Output off current LOW - The current flowing out of a disabled 3-state output with lozL a specified LOW output voltage applied.

**VOLTAGES** – All voltages are referenced to ground. Negative voltage limits are specified as absolute values (i.e., -10 V is greater than -1.0 V).

V<sub>CC</sub> Supply voltage – The range of power supply voltage over which the device is guaranteed to operate within the specified limits.

V<sub>CD(MAX)</sub> Input clamp diode voltage – The most negative voltage at an input when 18 mA is forced out of that input terminal. This parameter guarantees the integrity of the input diode which is intended to clamp negative ringing at the input terminal.

V<sub>IH</sub> Input HIGH voltage — The range of input voltages that represents a logic HIGH in the system.

V<sub>IH(MIN)</sub> Minimum input HIGH voltage — The minimum allowed input HIGH in a logic system. This value represents the guaranteed input HIGH threshold for the device.

V<sub>IL</sub> Input LOW voltage - The range of input voltages that represents a logic LOW in the system.

V<sub>IL(MAX)</sub> Maximum input LOW voltage – The maximum allowed input LOW in a system. This value represents the guaranteed input LOW threshold for the device.

V<sub>OH(MIN)</sub> Output HIGH voltage – The minimum voltage at an output terminal for the specified output current I<sub>OH</sub> and at the minimum value of V<sub>CC</sub>.

V<sub>OL(MAX)</sub> Output LOW Voltage - The maximum voltage at an output terminal sinking the maximum specified load current I<sub>OL</sub>.

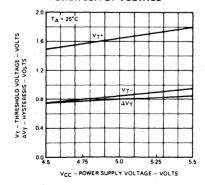

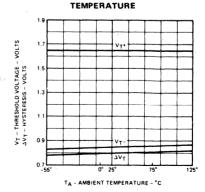

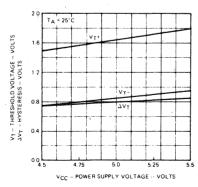

$V_{T+}$

**Positive-going threshold voltage** – The input voltage of a variable threshold device (i.e., Schmitt Trigger) that is interpreted as a  $V_{IH}$  as the input transition rises from below  $V_{T-(MIN)}$ .

$V_{T-}$  Negative-going threshold voltage – The input voltage of a variable threshold device (i.e., Schmitt Trigger) that is interpreted as a  $V_{IL}$  as the input transition falls from above  $V_{T+(MAX)}$ .

### **DEFINITION OF SYMBOLS AND TERMS USED IN THIS DATABOOK (Cont'd)**

#### AC SWITCHING PARAMETERS

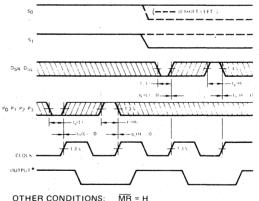

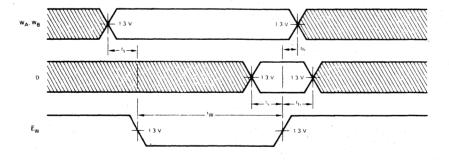

$t_s$

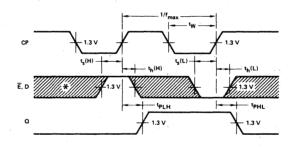

- f<sub>MAX</sub>

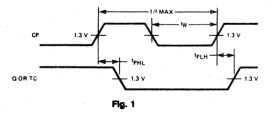

Toggle frequency/operating frequency The maximum rate at which clock pulses may be applied to a sequential circuit. Above this frequency the device may cease to function.

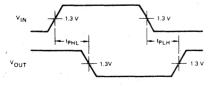

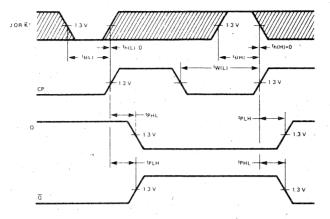

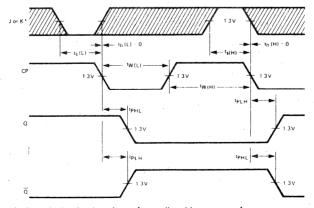

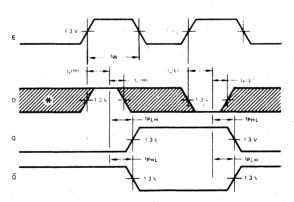

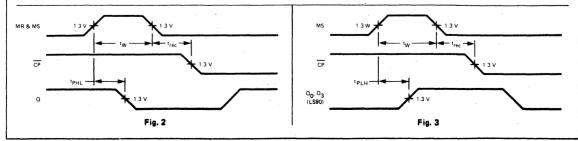

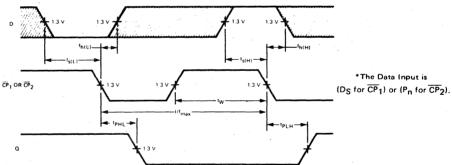

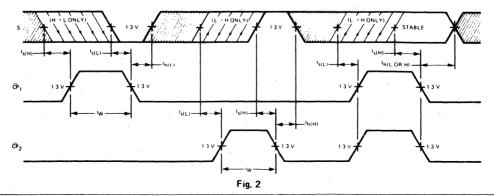

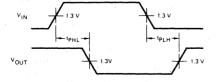

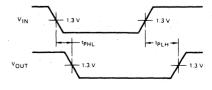

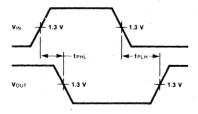

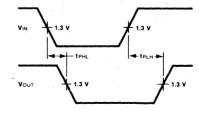

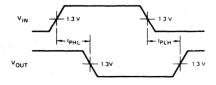

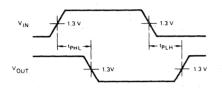

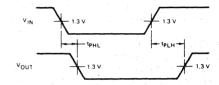

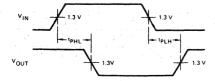

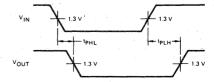

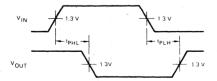

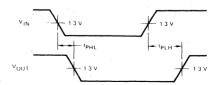

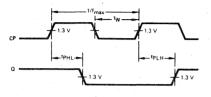

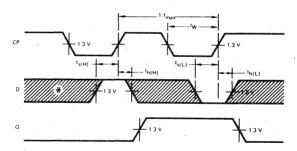

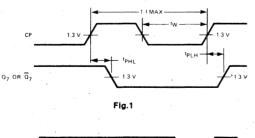

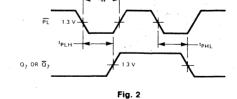

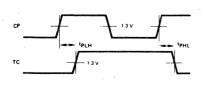

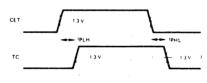

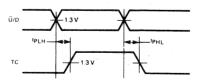

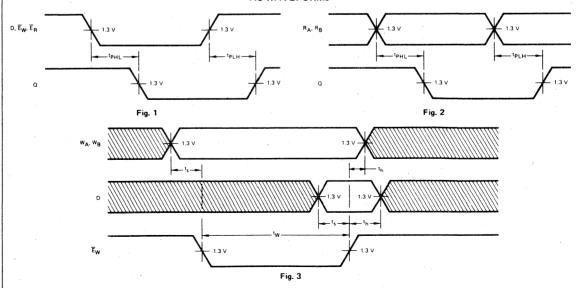

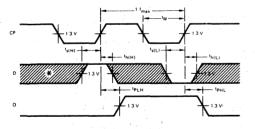

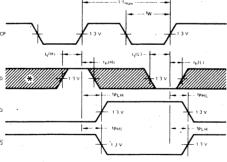

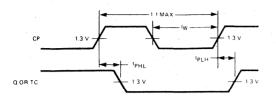

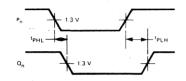

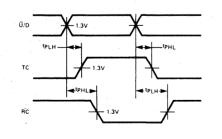

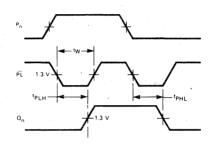

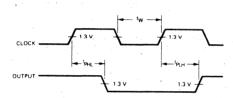

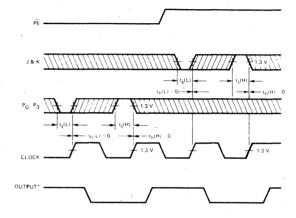

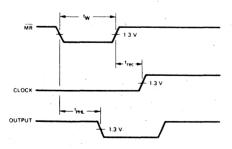

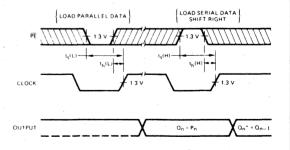

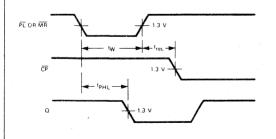

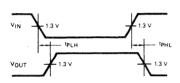

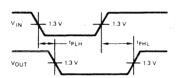

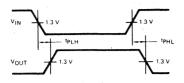

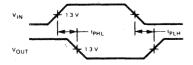

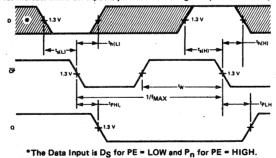

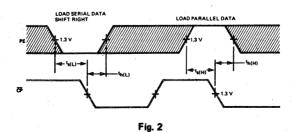

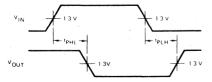

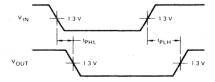

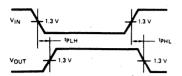

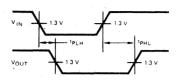

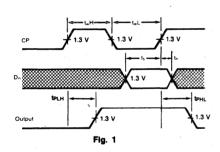

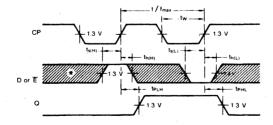

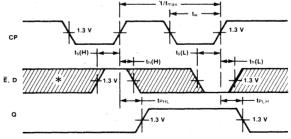

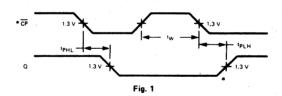

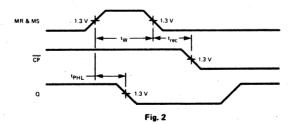

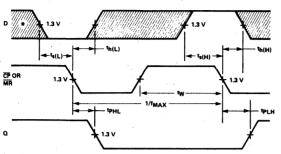

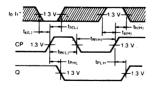

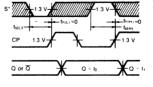

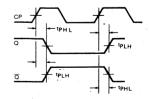

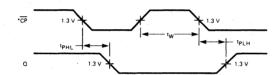

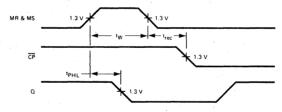

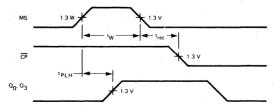

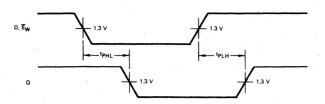

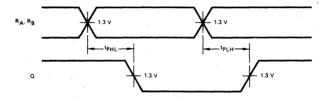

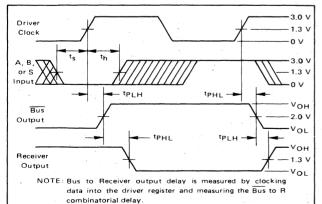

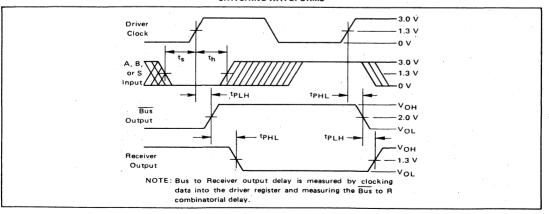

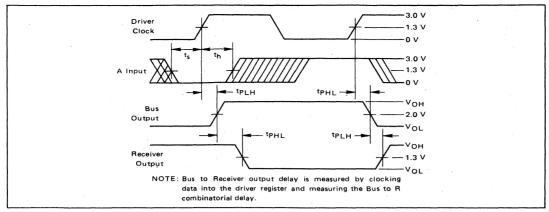

- t<sub>PLH</sub> **Propagation delay time** The time between the specified reference points, normally 1.3 V on the input and output voltage waveforms, with the output changing from the defined LOW level to the defined HIGH level.

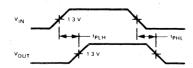

- t<sub>PHL</sub> **Propagation delay time** The time between the specified reference points, normally 1.3 V on the input and output voltage waveforms, with the output changing from the defined HIGH level to the defined LOW level.

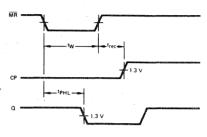

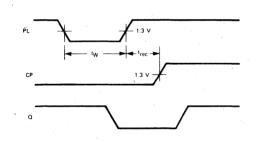

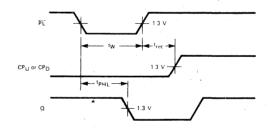

- t<sub>W</sub> Pulse width The time between 1.3 V amplitude points on the leading and trailing edges of a pulse.

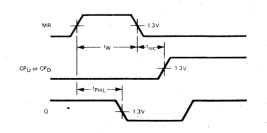

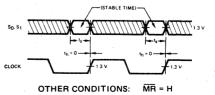

- th Hold time The interval immediately following the active transition of the timing pulse (usually the clock pulse) or following the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its continued recognition. A negative hold time indicates that the correct logic level may be released prior to the active transition of the timing pulse and still be recognized.

- **Set-up time** The interval immediately preceding the active transition of the timing pulse (usually the clock pulse) or preceding the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its recognition. A negative set-up time indicates that the correct logic level may be initiated sometime after the active transition of the timing pulse and still be recognized.

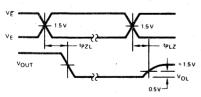

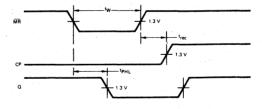

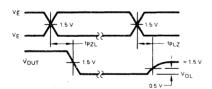

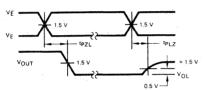

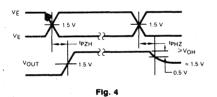

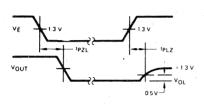

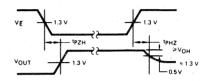

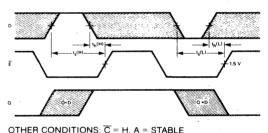

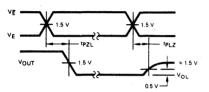

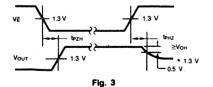

- t<sub>PHZ</sub>

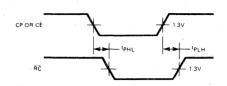

Output disable time (of a 3-state output) from HIGH level The time between the 1.3 V level on the input and a voltage 0.5 V below the steady state output HIGH level with the 3-state output changing from the defined HIGH level to a high-impedance (off) state.

- t<sub>PLZ</sub>

Output disable time (of a 3-state output) from LOW level The time between the 1.3 V level on the input and a voltage 0.5 V above the steady state output LOW level with the 3-state output changing from the defined LOW level to a high-impedance (off) state.

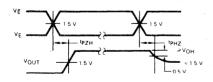

- t<sub>PZH</sub>

Output enable time (of a 3-state output) to a HIGH level The time between the 1.3 V levels of the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to a HIGH level.

- t<sub>PZL</sub>

Output enable time (of a 3-state output) to a LOW level The time between the 1.3 V levels of the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to a LOW level.

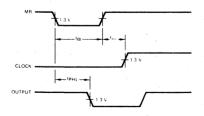

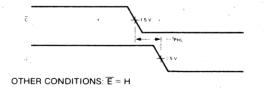

- t<sub>rec</sub> Recovery time The time between the 1.3 V level on the trailing edge of an asynchronous input control pulse and the 1.3 V level on a synchronous input (clock) pulse such that the device will respond to the synchronous input.

# **LOW POWER SCHOTTKY**

**Selection Information**

| Function                      | Low Power<br>Schottky<br>5 ns/2 mW | Std. TTL<br>54/74<br>10 ns/10 mW | High Speed<br>54H/74H<br>6 ns/22 mW | High Speed<br>Schottky<br>3 ns/19 mW |

|-------------------------------|------------------------------------|----------------------------------|-------------------------------------|--------------------------------------|

| NAND Gates                    |                                    |                                  |                                     |                                      |

| Hex Inverters                 | 54LS/74LS04                        | 54/7404                          | 54H/74H04                           | 54S/74S04                            |

| Hex Inverters (o. c.)         | 54LS/74LS05                        | 54/7405                          | 54H/74H05                           | 54S/74S05                            |

| Hex Schmitt<br>Trigger        | 54LS/74LS14                        | 54/7414                          |                                     |                                      |

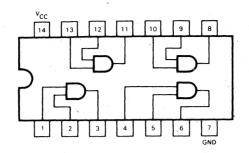

| Quad 2-Input                  | 54LS/74LS00                        | 54/7400                          | 54H/74H00                           | 54S/74S00                            |

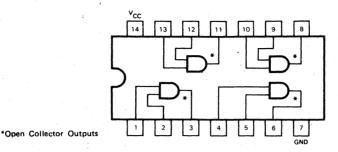

| Quad 2-Input<br>(o. c.)       | 54LS/74LS01                        | 54/7401                          | 54H/74H01                           |                                      |

| Quad 2-Input<br>(o. c.)       | 54LS/74LS03                        | 54/7403                          |                                     | 54S/74S03                            |

| Quad 2-Input<br>(48 mA)       | 54LS/74LS37                        | 54/7437                          |                                     |                                      |

| Quad 2-Input<br>(o. c. 48 mA) | 54LS/74LS38                        | 54/7438                          |                                     |                                      |

| Quad 2-Input<br>(o. c.⁄15 V)  | 54LS/74LS26                        |                                  |                                     |                                      |

| Quad 2-Input<br>Schmitt       | 54LS/74LS132                       | 54/74132                         |                                     | 54S/74S132                           |

| Triple 3-Input<br>(o. c.)     | 54LS/74LS12                        | 54/7412                          |                                     |                                      |

| Triple 3-Input                | 54LS/74LS10                        | 54/7410                          | 54H/74H10                           | 54S/74S10                            |

| Dual 4-Input<br>Schmitt       | 54LS/74LS13                        | 54/7413                          |                                     |                                      |

| Dual 4-Input                  | 54LS/74LS20                        | 54/7420                          | 54H/74H20                           | 54S/74S20                            |

| Dual 4-Input<br>(o. c.)       | 54LS/74LS22                        | 54/7422                          | 54H/74H22                           | 54S/74S22                            |

| Dual 4-Input<br>Buffer        | 54LS/74LS40                        | 54/7440                          | 54H/74H40                           | 54S/74S40                            |

| 8-Input                       | 54LS/74LS30                        | 54/7430                          | 54H/74H30                           | 54S/74S30                            |

| 13-Input                      | 54LS/74LS133                       |                                  |                                     | 54S/74S133                           |

| Function                  | Low Power<br>Schottky<br>5 ns/2 mW | Std. TTL<br>54/74<br>10 ns/10 mW | High Speed<br>54H/74H<br>6 ns/22 mW | High Speed<br>Schottky<br>3 ns/19 mW |

|---------------------------|------------------------------------|----------------------------------|-------------------------------------|--------------------------------------|

| NOR Gates                 |                                    |                                  |                                     | P                                    |

| Quad 2-Input              | 54LS/74LS02                        | 54/7402                          |                                     | 54S/74S02                            |

| Quad 2-Input<br>Buffer    | 54LS/74LS28                        |                                  |                                     |                                      |

| Quad 2-Input<br>(o. c.)   | 54LS/74LS33                        |                                  |                                     |                                      |

| Triple 3-Input            | 54LS/74LS27                        | 54/7427                          |                                     |                                      |

| Dual 5-Input              | 54LS/74LS260                       |                                  |                                     | 54S/74S260                           |

| AND Gates                 |                                    | ta Salata da A                   |                                     |                                      |

| Quad 2-Input              | 54LS/74LS08                        | 54/7408                          | 54H/74H08                           | 545/74508                            |

| Quad 2-Input<br>(o. c.)   | 54LS/74LS09                        | 54/7409                          | 54H/74H09                           | 54S/74S09                            |

| Triple 3-Input            | 54LS/74LS11                        | 54/7411                          | 54H/74H11                           | 54S/74S11                            |

| Triple 3-Input<br>(o. c.) | 54LS/74LS15                        |                                  | 54H/74H15                           | 54S/74S15                            |

| Dual 4-Input              | 54LS/74LS21                        | 54/7421                          | 54H/74H21                           | 54S/74S21                            |

| OR Gates                  |                                    |                                  |                                     |                                      |

| Dual 2-Input              | 54LS/74LS32                        | 54/7432                          |                                     | 54S/74S32                            |

| Exclusive OR Gate         |                                    |                                  |                                     | -                                    |

| Quad 2-Input              | 54LS/74LS86                        | 54/7486                          |                                     | 54S/74S86                            |

| Quad 2-Input              | 54LS/74LS386                       |                                  |                                     |                                      |

| Quad 2-Input<br>(o. c)    | 54LS/74LS136                       | )                                |                                     |                                      |

| Exclusive NOR Gate        |                                    |                                  |                                     |                                      |

| Quad 2-Input<br>(o. c.)   | 54LS/74LS266                       | 9386 (8242)                      |                                     |                                      |

| Function                                  | Low Power<br>Schottky<br>5 ns/2 mW | Std. TTL<br>54/74<br>10 ns/10 mW | High Speed<br>54H/74H<br>6 ns/22 mW | High Speed<br>Schottky<br>3 ns/19 mW |  |  |

|-------------------------------------------|------------------------------------|----------------------------------|-------------------------------------|--------------------------------------|--|--|

| AND-OR-INVERT GATES                       | *                                  |                                  |                                     |                                      |  |  |

| Dual 2-2-Input                            | 54LS/74LS51                        | 54/7451                          | 54H/74H51                           | 54S/74S51                            |  |  |

| 2-2-3-3-Input                             | 54LS/74LS54                        | <u></u> -                        | _                                   |                                      |  |  |

| 4-4-Input                                 | 54LS/74LS55                        | :                                |                                     | _                                    |  |  |

| BUFFERS (3-STATE)                         |                                    |                                  | <u></u>                             | <u> </u>                             |  |  |

| Quad 3-State LOW Enable                   | 54LS/74LS125A                      | 54/74125                         |                                     |                                      |  |  |

| Quad 3-State<br>HIGH Enable               | 54LS/74LS126A                      | 54/74126                         |                                     | _                                    |  |  |

| Hex Buffer<br>3-State<br>Common Enable    | 54LS/74LS365A                      | _                                | _                                   |                                      |  |  |

| Hex Inverting<br>3-State<br>Common Enable | 54LS/74LS366A                      |                                  |                                     | <del>-</del>                         |  |  |

| Hex Buffer<br>4-Bit & 2-Bit               | 54LS/74LS367A                      | <u></u>                          |                                     |                                      |  |  |

| Hex Inverting<br>4 Bit-&-2 Bit            | 54LS/74LS368A                      | <del></del>                      | _                                   | <u> </u>                             |  |  |

| Function        | Low Power<br>Schottky<br>5 ns/2 mW | Std. TTL<br>54/74<br>10 ns/10 mW | High Speed<br>54H/74H<br>6 ns/22 mW | High Speed<br>Schottky<br>3 ns/19 mW |  |  |

|-----------------|------------------------------------|----------------------------------|-------------------------------------|--------------------------------------|--|--|

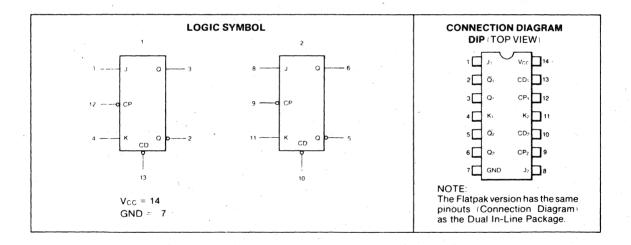

| DUAL FLIP-FLOPS |                                    |                                  |                                     |                                      |  |  |

| Dual JK         | (54LS/74LS73)A                     | (54/7473)                        | 54H/74H73                           |                                      |  |  |

| Dual JK         | 54LS/74LS76A                       | 54/7476                          | 54H/74H76                           |                                      |  |  |

| Dual JK         | 54LS/74LS78A                       |                                  | 54H/74H78                           |                                      |  |  |

| Dual JK         | 54LS/74LS107A                      | 54/74107                         |                                     |                                      |  |  |

| Dual JK         | 54LS/74LS109A                      | 9024                             |                                     | 54S/74S109                           |  |  |

| Dual JK         | 54LS/74LS112A                      |                                  |                                     | 54S/74S112                           |  |  |

| Dual JK         | 54LS/74LS113A                      |                                  |                                     | 548748113                            |  |  |

| Dual JK         | 54LS/74LS114A                      |                                  |                                     | 54S/74S114                           |  |  |

| Dual D          | 54LS/74LS74A                       | 54/7474                          | 54H/74H74                           | 545/74574                            |  |  |

### MONOSTABLE MULTIVIBRATORS WITH SCHMITT-TRIGGER INPUTS

| Description | Device No.   | No. of Inputs |          | Output      | Typ. Power  |  |

|-------------|--------------|---------------|----------|-------------|-------------|--|

|             | Device No.   | Positive      | Negative | Pulse Range | Dissipation |  |

| Dual        | 54LS/74LS221 | 1             | 1        | 20 ns-70 s  | 23 mW       |  |

### RETRIGGERABLE MONOSTABLE MULTIVIBRATORS

| Description | Davis a Na   | No. of Inputs |          | Output      | Typ. Power  |

|-------------|--------------|---------------|----------|-------------|-------------|

|             | Device No.   | Positive      | Negative | Pulse Range | Dissipation |

| Single      | 74LS/54LS122 | 2             | 2        | 45 ns-∞     | 30 mW       |

| Dual        | 74LS/54LS123 | 1             | 1        | 45 ns-∞     | 60 mW       |

| Counters  A= Asynchronous S = Synchronous |               |                   |               |                  |                             |                                     |                               |

|-------------------------------------------|---------------|-------------------|---------------|------------------|-----------------------------|-------------------------------------|-------------------------------|

| Function                                  | DEVICE NO.    | Modulo            | Parallel Load | Clock Transition | Max Clock Rate<br>MHz (typ) | Clock to Q Output<br>Delay ns (typ) | Power Dissipation<br>mW (typ) |

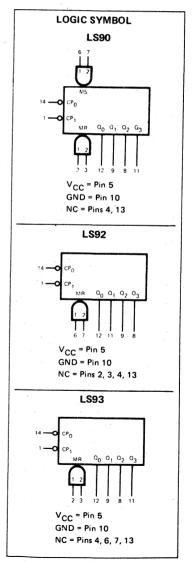

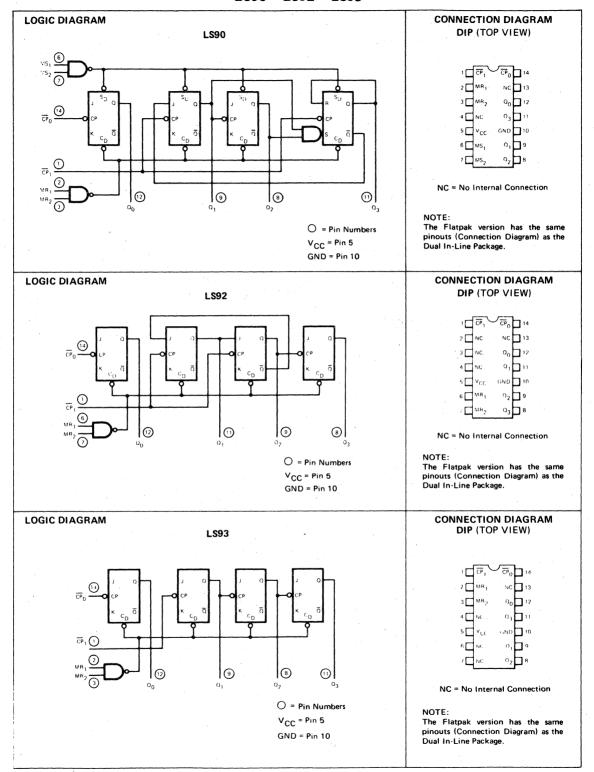

| Asynchronous                              | 54LS/74LS90   | 2x5               |               | 1                | 50                          | 33                                  | 45                            |

| Asynchronous                              | 54LS/74LS92   | 2x6               |               | 1                | 50                          | 33                                  | 45                            |

| Asynchronous                              | 54LS/74LS93   | 2x8               |               | 1                | 50                          | 46                                  | 45                            |

| Asynchronous                              | 54LS/74LS196  | 2x5               | Α             | tī               | 60                          | 48                                  | 60                            |

| Asynchronous                              | 54LS/74LS197  | 2×8               | Α             | 1                | 70                          | 60                                  | 60                            |

| Asynchronous                              | 54LS/74LS290  | 2x5               |               | 1                | 50                          | . 10                                | 45                            |

| Asynchronous                              | 54LS/74LS293  | 2×8               |               | 1                | 50                          | 10                                  | 45                            |

| Asynchronous                              | 54LS/74LS390  | 2x5<br>2x5        |               | 1                | 50                          | 10                                  | 100                           |

| Asynchronous                              | 54LS/74LS393  | 2x8<br>2x8        |               | 1                | 50                          | 10                                  | 100                           |

| Asynchronous                              | 54LS/74LS490  | 2x5<br>2x5        |               | L                | 50                          | 6                                   | 100                           |

| Synchronous                               | 54LS/74LS160A | 10<br>Presettable | S             |                  | 45                          | 15                                  | 95                            |

| Synchronous                               | 54LS/74LS161A | 16<br>Presettable | S             | J                | 45                          | 15                                  | 95                            |

| Synchronous                               | 54LS/74LS162A | 10<br>Presettable | S             |                  | 45                          | 15                                  | 95                            |

| Synchronous                               | 54LS/74LS163A | 16<br>Presettable | S             |                  | 45                          | 15                                  | 95                            |

| Up/Down                                   | 54LS/74LS168  | 10<br>Presettable | S             | <u></u>          | 32                          | 15                                  | 100                           |

| Up/Down                                   | 54LS/74LS169  | 16<br>Presettable | S             |                  | 32                          | 15                                  | 100                           |

| Up/Down                                   | 54LS/74LS190  | 10                | Α             | J                | 40                          | 20                                  | 90                            |

| Up/Down                                   | 54LS/74LS191  | 16                | Α             |                  | 40                          | 20                                  | 90                            |

| Up/Down                                   | 54LS/74LS192  | 10                | Α             |                  | 40                          | 30                                  | 85                            |

| Up/Down                                   | 54LS/74LS193  | 16                | Α             | Ţ                | 40                          | 30                                  | 85                            |

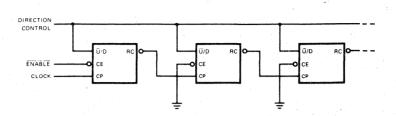

| Up/Down                                   | 54LS/74LS568  |                   | S             | 1                | 35                          |                                     | 147                           |

| Up/Down                                   | 54LS/74LS569  |                   | S             | Ţ                | 35                          |                                     | 147                           |

### **ARITHMETIC OPERATORS**

(CLA = Carry Lookahead)

| Function                  | Device No.   | Description               | No. of Bits | Typical<br>tpd ns | Power Dissipation<br>mW (typ) |

|---------------------------|--------------|---------------------------|-------------|-------------------|-------------------------------|

| Adder                     | 54LS/74LS83A | Full Binary 4-Bit w/Carry | 4           | 15                | 95                            |

| Adder                     | 54LS/74LS283 | Full Binary 4-Bit w/Carry | 4           | 15                | 95                            |

| Arithmetic Logic Unit     | 54LS/74LS181 | ALU with External CLA     | 4           | 20                | 105                           |

| Carry Lookahead Generator | 54LS/74LS182 | Carry Lookahead           | _           |                   | 1 -                           |

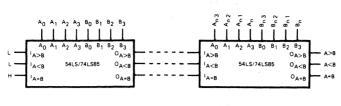

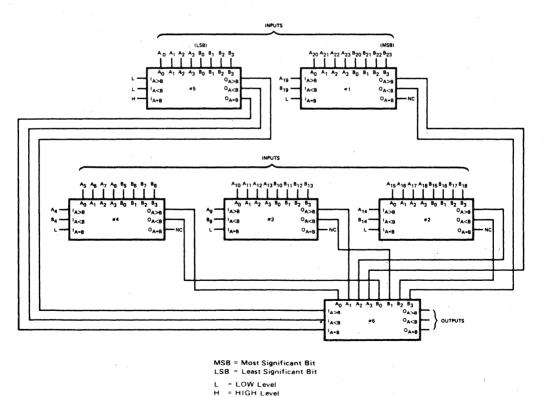

### COMPARATORS

| Description                   | Device No.  | Typical Compare Time | Typical Total Power Dissipation |

|-------------------------------|-------------|----------------------|---------------------------------|

| 4-Bit Magnitude<br>Comparator | 54LS/74LS85 | 23.5 ns              | 52 mW                           |

### **RANDOM-ACCESS READ-WRITE MEMORIES**

| Description  | Device No.   | Type of Output | Organization | Typical Address<br>Time |

|--------------|--------------|----------------|--------------|-------------------------|

| 64 Bit Array | 54LS/74LS89  | o.c.           | 16 x 4       |                         |

| 64 Bit Array | 54LS/74LS189 | 3-State        | 16 x 4       |                         |

| 64 Bit Array | 54LS/74LS289 | o.c.           | 16 x 4       |                         |

### **CLOCK GENERATOR CIRCUITS**

| Description                              | Device No.   | Typical Power Dissipation |  |

|------------------------------------------|--------------|---------------------------|--|

| Dual VCO with Enable                     | 54LS/74LS124 | 90 mW                     |  |

| Dual Voltage Controlled Osc. with Enable | 54LS/74LS326 | 90 mW                     |  |

| Dual VCO                                 | 54LS/74LS325 | 150 mW                    |  |

| Dual VCO                                 | 54LS/74LS327 | 150 mW                    |  |

| Voltage Controlled Osc. with Enable      | 54LS/74LS324 | 90 mW                     |  |

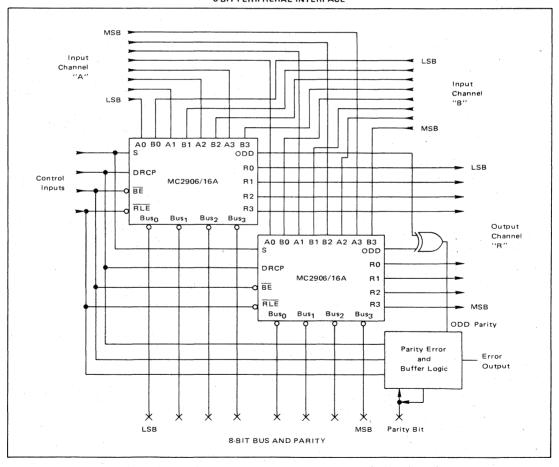

### PARITY GENERATOR/CHECKER

| Description                                | Device No.   | Typical Time Delay | Typical Power Dissipation |

|--------------------------------------------|--------------|--------------------|---------------------------|

| 9-Bit Odd/Even Parity<br>Generator/Checker | 54LS/74LS280 | 31 ns              | 80 mW                     |

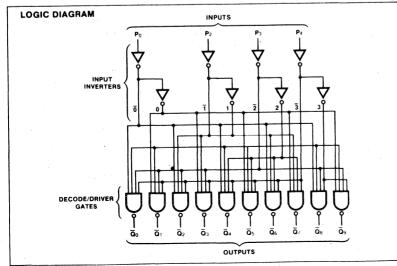

# DECODER/DEMULTIPLEXERS Unit Load (UL) = 40 µA HIGH/1.6 mA LOW

| Olit Loss (of) — 40 kg illes to the Low |              |                |                      |                       |                                  |                           |                          |                                  |              |

|-----------------------------------------|--------------|----------------|----------------------|-----------------------|----------------------------------|---------------------------|--------------------------|----------------------------------|--------------|

| Function                                | Device No.   | Address Inputs | Active LOW<br>Enable | Active LOW<br>Outputs | Open Collector<br>Output Voltage | Address Delay<br>ns (typ) | Enable Delay<br>ns (typ) | Power<br>Dissipation<br>mW (typ) | Fan-out (UL) |

| Dual 1-of-4                             | 54LS/74LS139 | 2+2            | . 1+1                | 4+4                   |                                  | 22                        | 19                       | 34                               | 5            |

| Dual 1-of-4                             | 54LS/74LS155 | 2              | 2+2                  | 4+4                   |                                  | 18                        | 15                       | 30                               | 5            |

| Dual 1-of-4                             | 54LS/74LS156 | 2              | 2+2                  | 4+4                   | 5.5 V                            | 33                        | 26                       | 31                               | 5            |

| Dual 1-of-4                             | 54LS/74LS256 | 2+2            | 1                    | 4+4                   |                                  | 30                        | 19                       | 60                               | 5            |

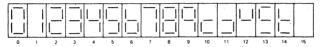

| BCD to<br>7-Segment                     | 54LS/74LS47  | 4              |                      | 7                     | 15 V                             | 50                        | _                        | 35                               | 15           |

| BCD to<br>7-Segment                     | 54LS/74LS48  | 4              | _                    | 7                     | 5.5 V                            | 50                        | _                        | 125                              | 4            |

| BCD to<br>7-Segment                     | 54LS/74LS49  | 4              | _                    | 7                     | 5.5 V                            | 50                        | _                        | 40                               | 5            |

| BCD to<br>7-Segment                     | 54LS/74LS247 | 4              |                      | 7                     | 15 V                             | 50                        | _                        | 35                               | 15           |

| BCD to<br>7-Segment                     | 54LS/74LS248 | 4              | _                    | 7                     | 5.5 V                            | 50                        | _                        | 125                              | 4            |

| BCD to<br>7-Segment                     | 54LS/74LS249 | 4              | _                    |                       | 5.5 V                            | 50                        | _                        | 40                               | 5            |

| 1-of-8                                  | 54LS/74LS259 | 3              | 1                    | 8                     |                                  | 30                        | 19                       | 60                               | 5            |

| 1-of-8                                  | 54LS/74LS42  | 3              | 1                    | 8                     |                                  | 17                        | 17                       | 35                               | 5            |